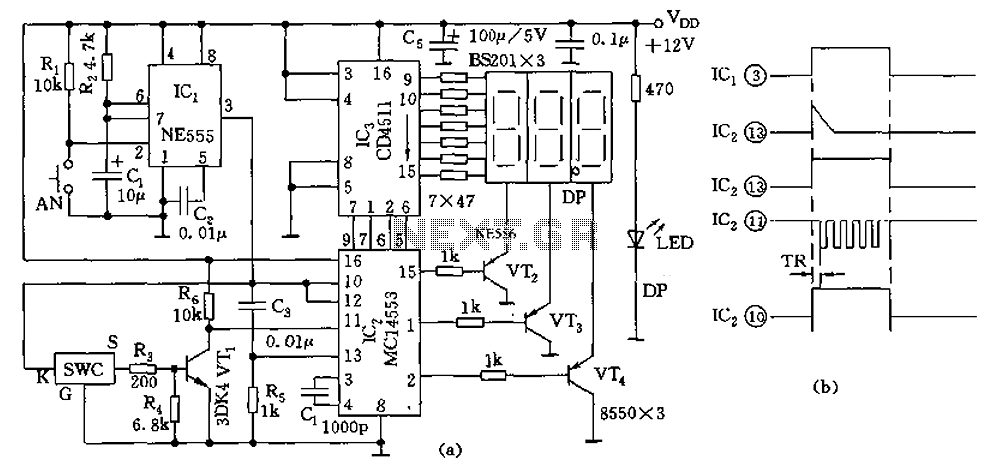

Digital sine wave generator

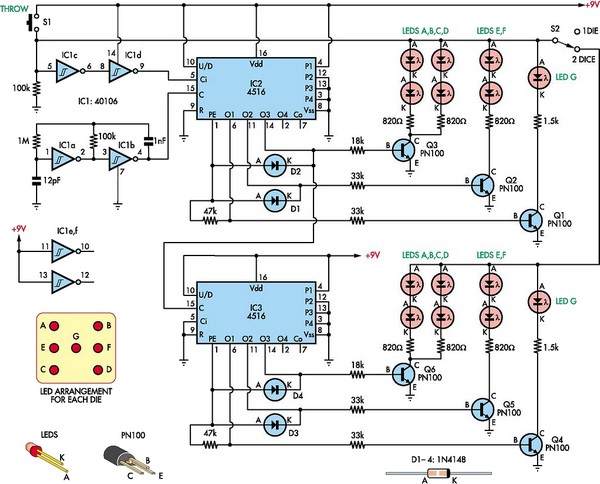

By utilizing a reverse binary counter along with a binary-coded decimal (BCD) decoder, a step voltage can be generated, which can then be approximated to produce a sine wave signal with adequate accuracy for various applications. In the digital generator circuit diagram, resistors R1 to R9 are employed to generate the first quarter of the sine wave while the reverse counter D2 operates in normal counting mode. The trigger, consisting of two logic gates D1.3 and D1.4, activates when the outputs "0" or "9" of decoder D3 transition to logic zero, thereby controlling the operational mode (reverse or normal) of the reverse counter. Consequently, for every twenty clock ticks at the generator's input, the output of summing operational amplifier A1 will yield the positive half-wave of the sine wave. The negative half-wave is generated in the subsequent twenty cycles by inverting the positive half-wave using amplifier A2, which alternates its operation (the first twenty cycles as a non-inverting amplifier and the next twenty cycles as an inverting amplifier). The gain of the amplifier is switched by the FET transistor V4 from -1 to +1. The signal from the output of the RS flip-flop (D1.3, D1.4) passes through the D flip-flop D6 and the Zener diode V1 to the transistors V1 and V2, which form a level shifting circuit, before reaching the gate of the FET transistor V4. The voltage from the wiper of potentiometer R13 is adjusted to ensure zero voltage at the output of summing amplifier A1 when all outputs of the counter D2 are at logic zero.

The circuit design described integrates several key components to achieve a sine wave output through a systematic approach. The reverse binary counter D2 is responsible for counting in reverse, which is crucial for generating the desired waveform. The binary-coded decimal decoder D3 decodes the counter's output into a format that can trigger the logic gates, specifically D1.3 and D1.4. These gates function as a control mechanism, switching the operational mode of the counter based on specific output conditions.

The resistors R1 to R9 play a vital role in shaping the initial quarter of the sine wave, ensuring that the output signal begins accurately. The summing operational amplifier A1 is central to the process, as it combines the outputs from the resistors to create the positive half of the sine wave. The subsequent negative half-wave is achieved through the use of amplifier A2, which alternates its configuration based on the timing of the input cycles, effectively ensuring that the waveform is continuous and smooth.

The gain control provided by FET transistor V4 is an essential feature, allowing for dynamic adjustment of the output signal's amplitude. The circuit's feedback mechanism, which includes the level shifting transistors V1 and V2, ensures that the signal remains within acceptable voltage ranges, thereby preventing distortion and maintaining fidelity in the output waveform.

The use of a potentiometer R13 for fine-tuning the output voltage further enhances the circuit's usability, enabling precise adjustments to achieve the desired output characteristics. This comprehensive design allows for the effective generation of sine wave signals suitable for various applications in electronic systems.By using the reverse binary counter and the binary-coded decimal decoder can obtained the step voltage, and by approximating this voltage can be produced the sine wave signal with sufficient accuracy, suitable for many purposes. In the circuit diagram of the digital generator (see figure 1) the resistors R1. R9 is used to produce the first quarter of the sine wave (while the reverse counter D2 has normal counting mode) as the current, applied to the inverting input of the summing operational amplifier A1. The trigger, composed of the two logic gates D1. 3 and D1. 4 will be switched when the outputs "0" or "9" of the decoder D3 changes to logic zero, this trigger controls the mode (reverse or normal) of the reverse counter.

Thus, for twenty clock ticks at the input of the generator, the output of the summing amplifier A1 will create the positive half-wave sine wave. The negative half-wave will be formed within the next twenty cycles by inverting the positive half-wave with the amplifier A2, which operates alternately (the first 20 cycles the amplifier A2 works as the non inverter, the next 20 cycles it works as the inverter).

The gain of the amplifier switches by the FET transistor V4 from -1 to +1. The signal from the output of RS flip-flop (D1. 3, D1. 4) feeds through the D flip-flop D6 and the zener diode V1 to the transistors V1 and V2 (level shifting circuit) and further on the gate of the FET transistor V4. The voltage taken from the wiper of potentiometer R13, is adjusted to get zero voltage at output of the summing amplifier A1 while all outputs of the counter D2 has logic zero.

🔗 External reference

The circuit design described integrates several key components to achieve a sine wave output through a systematic approach. The reverse binary counter D2 is responsible for counting in reverse, which is crucial for generating the desired waveform. The binary-coded decimal decoder D3 decodes the counter's output into a format that can trigger the logic gates, specifically D1.3 and D1.4. These gates function as a control mechanism, switching the operational mode of the counter based on specific output conditions.

The resistors R1 to R9 play a vital role in shaping the initial quarter of the sine wave, ensuring that the output signal begins accurately. The summing operational amplifier A1 is central to the process, as it combines the outputs from the resistors to create the positive half of the sine wave. The subsequent negative half-wave is achieved through the use of amplifier A2, which alternates its configuration based on the timing of the input cycles, effectively ensuring that the waveform is continuous and smooth.

The gain control provided by FET transistor V4 is an essential feature, allowing for dynamic adjustment of the output signal's amplitude. The circuit's feedback mechanism, which includes the level shifting transistors V1 and V2, ensures that the signal remains within acceptable voltage ranges, thereby preventing distortion and maintaining fidelity in the output waveform.

The use of a potentiometer R13 for fine-tuning the output voltage further enhances the circuit's usability, enabling precise adjustments to achieve the desired output characteristics. This comprehensive design allows for the effective generation of sine wave signals suitable for various applications in electronic systems.By using the reverse binary counter and the binary-coded decimal decoder can obtained the step voltage, and by approximating this voltage can be produced the sine wave signal with sufficient accuracy, suitable for many purposes. In the circuit diagram of the digital generator (see figure 1) the resistors R1. R9 is used to produce the first quarter of the sine wave (while the reverse counter D2 has normal counting mode) as the current, applied to the inverting input of the summing operational amplifier A1. The trigger, composed of the two logic gates D1. 3 and D1. 4 will be switched when the outputs "0" or "9" of the decoder D3 changes to logic zero, this trigger controls the mode (reverse or normal) of the reverse counter.

Thus, for twenty clock ticks at the input of the generator, the output of the summing amplifier A1 will create the positive half-wave sine wave. The negative half-wave will be formed within the next twenty cycles by inverting the positive half-wave with the amplifier A2, which operates alternately (the first 20 cycles the amplifier A2 works as the non inverter, the next 20 cycles it works as the inverter).

The gain of the amplifier switches by the FET transistor V4 from -1 to +1. The signal from the output of RS flip-flop (D1. 3, D1. 4) feeds through the D flip-flop D6 and the zener diode V1 to the transistors V1 and V2 (level shifting circuit) and further on the gate of the FET transistor V4. The voltage taken from the wiper of potentiometer R13, is adjusted to get zero voltage at output of the summing amplifier A1 while all outputs of the counter D2 has logic zero.

🔗 External reference