FPGA-based fingerprint identification system schematic

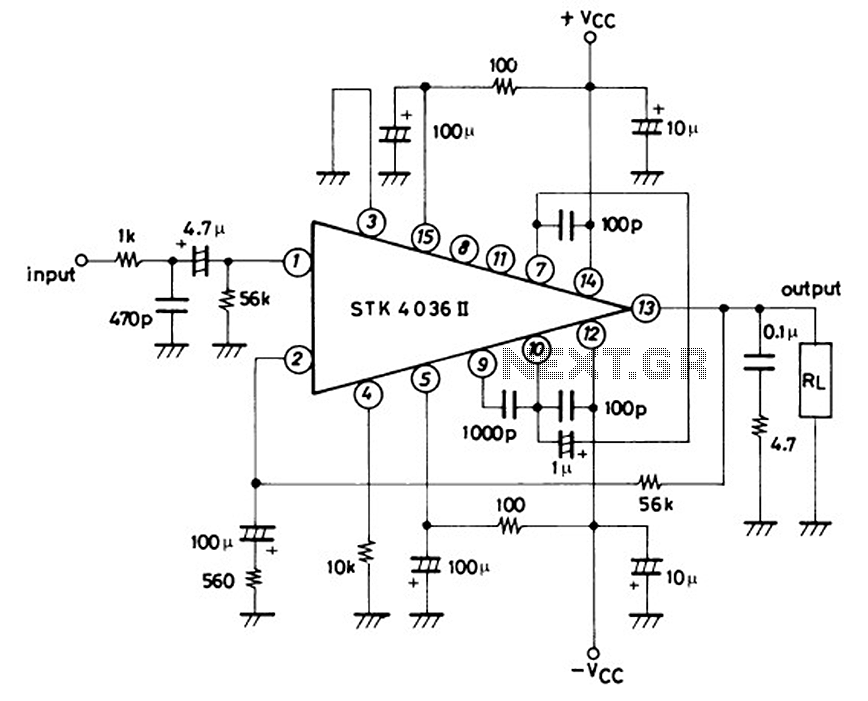

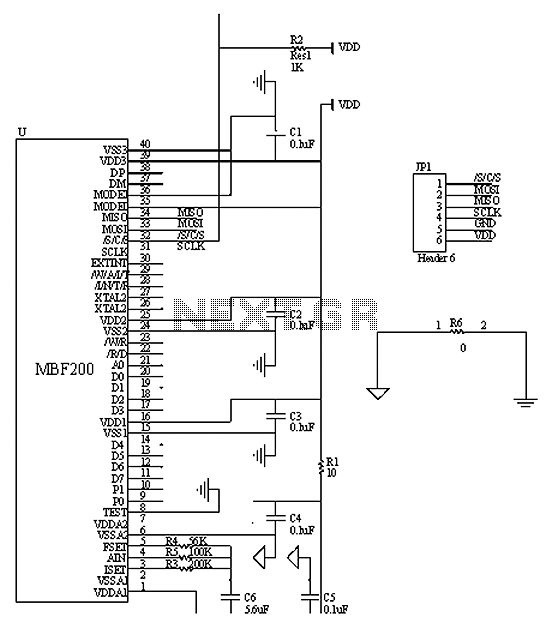

The ASIC design focuses on a highly integrated, low-power solution with a short development cycle to complete an FPGA design aimed at achieving a robust background system, which holds significant practical relevance and broad market potential. The project utilizes the Xilinx Spartan 3E FPGA family as the core control device, leveraging advanced 90nm technology with a maximum capacity of 500,000 gates to support a 32-bit RISC processor paired with 128 Mbit Parallel Flash, adequately meeting design specifications. The system manages an embedded soft-core implementation using hardware recognition algorithms to ensure the integrity and validity of the identification system's functions. A Fujitsu MBF200 fingerprint sensor is incorporated, communicating with the FPGA via SPI mode through four connections: MISO, MOSI, /S/C/S, and SCLK. The /S/C/S serves as the MBF200 enable pin, while SCLK acts as the system clock. To initiate fingerprint signal processing, the FPGA drives /S/C/S low, activating the MBF200. Control commands are sent from the FPGA to the MBF200 through the MOSI line to dictate data output and transmission modes. VDD [3:1] provides digital power input, VDDA [2:1] serves as the analog power supply, VSS [3:1] is designated as the digital ground, and VSSA [2:1] is for analog ground, as illustrated in the accompanying figure. To mitigate interference between digital and analog signals, a 10-ohm resistor is used for separation, and capacitors are connected between the input and the corresponding digital supply and ground to filter out DC signals. Additionally, a 0-ohm isolation strategy is employed to prevent interference between digital signals and ground, effectively limiting loop current and suppressing noise across all frequency bands. The MODE [1:0] pins are configured to set the interface mode for the MBF200, with a setting of 01 selecting the SPI transmission mode. In this SPI mode, the AIN, ISET, and FEST interfaces are not utilized; however, it is advisable to connect resistors to ground based on the internal circuit structure of the MBF200.

The design effectively integrates a high-performance fingerprint recognition system using the Xilinx Spartan 3E FPGA and the Fujitsu MBF200 sensor. The FPGA serves as the central processing unit, executing complex algorithms for fingerprint recognition while managing data flow to and from the MBF200 sensor. The selection of SPI communication ensures efficient data transfer, minimizing latency in fingerprint processing. The use of low-power components aligns with modern design principles aimed at energy efficiency, making the system suitable for portable applications.

The implementation of power and ground management is critical in this design. By utilizing dedicated power inputs for digital and analog components, the potential for signal interference is significantly reduced. The inclusion of resistors and capacitors in the design serves to filter out noise and stabilize the power supply, ensuring reliable operation of the fingerprint sensor.

Furthermore, the choice of a 0-ohm resistor for isolation reflects a thoughtful approach to managing electromagnetic interference (EMI) and maintaining signal integrity. This design decision enhances the overall performance of the system, allowing for robust operation even in environments with varying electronic noise levels.

Overall, the project exemplifies a well-rounded approach to ASIC design, emphasizing integration, power efficiency, and signal integrity, which are essential for the successful deployment of advanced fingerprint recognition systems in a competitive market.ASIC design choosing highly integrated, low-power, short development cycle to complete this FPGA design to achieve a system of background, has a strong practical significance a nd broad market space. Companies using xilinx Spartan 3E FPGA family as the core control device, this device uses 90ns advanced technology, the maximum capacity of 500,000 to support 32-bit RISC processor with 128 Mbit Parallel Flash, sufficient to meet the design requirements. The project used to manage embedded soft-core implementation of the system using hardware recognition algorithms to ensure the integrity and validity of the identification system functions.

The design uses a Fujitsu MBF200 fingerprint sensor, MBF200 hardware block diagram shown in Figure 6, the use of SPI mode, so MBF200 and FPGA only through MISO, MOSI,/S/C/S, SCLK four ports are connected./S/C/S is MBF200 enable terminal, SCLK is MBF200 system clock when required fingerprint signal, FPGA to/S/C/S to send low level, MBF200 work. FPGA through MOSI MBF200 to send control commands to control MBF200 data output mode and the transmission mode.

VDD [3: 1] as a digital power input, VDDA [2: 1] as an analog power supply input, VSS [3: 1] is the digital ground, VSSA [2: 1] to analog, so the connection shown in Figure. In order to prevent interference with the digital signal analog signal with a 10 ohm resistor separated.

And it is also connected between the input and the corresponding digital supply digital ground capacitance to the Court unless the DC signal. In order to prevent interference with digital signals between the ground, the design uses 0 ohm isolation.

0 ohm current path corresponds to a very narrow, can effectively limit the loop current, the noise is suppressed. Has a damping effect on the resistance in all frequency bands (0 ohm impedance there), this is stronger than the magnetic beads.

MODE [1: 0] pins are used to set the interface mode MBF200 used in this design, set MODE [1: 0] is 01, SPI transmission mode is selected. In SPI mode which, AIN, ISET, FEST three interfaces will not spend, but according MBF200 internal circuit structure, preferably resistor connected to ground.

The design effectively integrates a high-performance fingerprint recognition system using the Xilinx Spartan 3E FPGA and the Fujitsu MBF200 sensor. The FPGA serves as the central processing unit, executing complex algorithms for fingerprint recognition while managing data flow to and from the MBF200 sensor. The selection of SPI communication ensures efficient data transfer, minimizing latency in fingerprint processing. The use of low-power components aligns with modern design principles aimed at energy efficiency, making the system suitable for portable applications.

The implementation of power and ground management is critical in this design. By utilizing dedicated power inputs for digital and analog components, the potential for signal interference is significantly reduced. The inclusion of resistors and capacitors in the design serves to filter out noise and stabilize the power supply, ensuring reliable operation of the fingerprint sensor.

Furthermore, the choice of a 0-ohm resistor for isolation reflects a thoughtful approach to managing electromagnetic interference (EMI) and maintaining signal integrity. This design decision enhances the overall performance of the system, allowing for robust operation even in environments with varying electronic noise levels.

Overall, the project exemplifies a well-rounded approach to ASIC design, emphasizing integration, power efficiency, and signal integrity, which are essential for the successful deployment of advanced fingerprint recognition systems in a competitive market.ASIC design choosing highly integrated, low-power, short development cycle to complete this FPGA design to achieve a system of background, has a strong practical significance a nd broad market space. Companies using xilinx Spartan 3E FPGA family as the core control device, this device uses 90ns advanced technology, the maximum capacity of 500,000 to support 32-bit RISC processor with 128 Mbit Parallel Flash, sufficient to meet the design requirements. The project used to manage embedded soft-core implementation of the system using hardware recognition algorithms to ensure the integrity and validity of the identification system functions.

The design uses a Fujitsu MBF200 fingerprint sensor, MBF200 hardware block diagram shown in Figure 6, the use of SPI mode, so MBF200 and FPGA only through MISO, MOSI,/S/C/S, SCLK four ports are connected./S/C/S is MBF200 enable terminal, SCLK is MBF200 system clock when required fingerprint signal, FPGA to/S/C/S to send low level, MBF200 work. FPGA through MOSI MBF200 to send control commands to control MBF200 data output mode and the transmission mode.

VDD [3: 1] as a digital power input, VDDA [2: 1] as an analog power supply input, VSS [3: 1] is the digital ground, VSSA [2: 1] to analog, so the connection shown in Figure. In order to prevent interference with the digital signal analog signal with a 10 ohm resistor separated.

And it is also connected between the input and the corresponding digital supply digital ground capacitance to the Court unless the DC signal. In order to prevent interference with digital signals between the ground, the design uses 0 ohm isolation.

0 ohm current path corresponds to a very narrow, can effectively limit the loop current, the noise is suppressed. Has a damping effect on the resistance in all frequency bands (0 ohm impedance there), this is stronger than the magnetic beads.

MODE [1: 0] pins are used to set the interface mode MBF200 used in this design, set MODE [1: 0] is 01, SPI transmission mode is selected. In SPI mode which, AIN, ISET, FEST three interfaces will not spend, but according MBF200 internal circuit structure, preferably resistor connected to ground.