Frequency-to-voltage converter

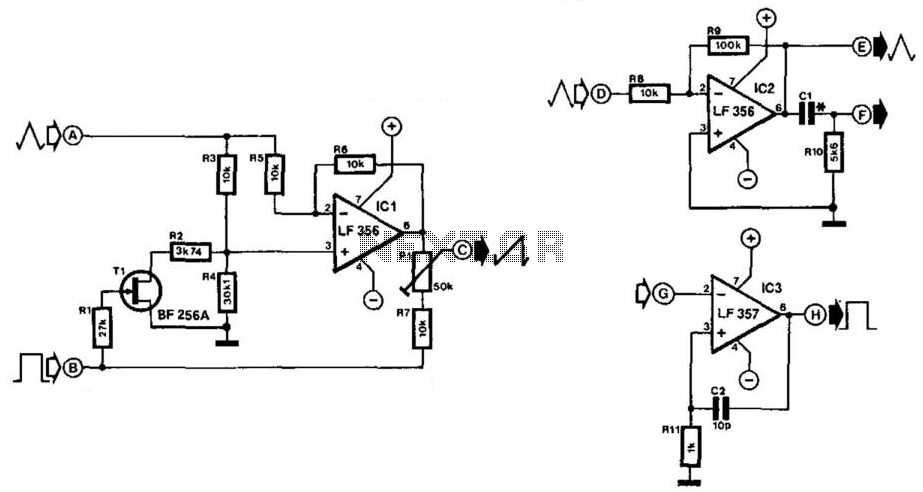

In these applications, a pulse input at a specified percentage is differentiated by a capacitor-resistor (C-R) network. The negative-going edge at pin 6 triggers the input comparator, activating the timer circuit. Similar to a voltage-to-frequency (V-to-F) converter, the average current flowing out of pin 1 is given by I_average = i (1.1 RjC^ f). In this simple circuit, the current is filtered through a network consisting of a 100 kΩ resistor and a 1 µF capacitor. The ripple will be less than 10 mV peak; however, the response will be slow, characterized by a time constant of 0.1 seconds and settling time of 0.7 seconds to 0.1%.

In this circuit design, the pulse input is processed through a differentiating C-R network, which serves to convert the input pulse into a sharp negative-going edge. This edge is crucial for triggering the comparator connected to pin 6, which subsequently activates the timer circuit. The design utilizes a voltage-to-frequency conversion principle, where the average current (I_average) flowing from pin 1 is calculated based on the equation I_average = i (1.1 RjC^ f). This indicates a direct relationship between the input current, resistance, capacitance, and frequency of operation.

The filtering component of the circuit consists of a resistor (RL) with a resistance of 100 kΩ and a capacitor (C) of 1 µF. This RC filter is designed to smooth out the output current, ensuring that any high-frequency noise is attenuated. As a result, the ripple voltage at the output is maintained below 10 mV peak, which is critical for applications requiring precision and stability in the output signal.

However, the circuit exhibits a slow response time, characterized by a time constant of 0.1 seconds. This indicates that the circuit will take this duration to respond to changes in the input signal. Furthermore, the settling time of 0.7 seconds to reach within 0.1% of the final value suggests that while the circuit is stable, it may not be suitable for applications requiring rapid response times. Overall, this design balances filtering and stability, making it appropriate for specific applications where precision is paramount, but speed is not the primary concern.In these applications, a pulse input at % is differentiated by a C-R network and the negative-going edge at pin 6 causes the input comparator to trigger the timer circuit. Just as with a V-to-F converter, the average current flowing out of pin 1 is IaverAGE = i (1.1 RjC^ f.

In this simple circuit, this current is filtered in the network RL = 100 k ohm and 1 µF. The ripple will be less than 10 mV peak, but the response will be slow, with a 0.1 second time constant, and settling of 0.7 second to 0.1%

In this circuit design, the pulse input is processed through a differentiating C-R network, which serves to convert the input pulse into a sharp negative-going edge. This edge is crucial for triggering the comparator connected to pin 6, which subsequently activates the timer circuit. The design utilizes a voltage-to-frequency conversion principle, where the average current (I_average) flowing from pin 1 is calculated based on the equation I_average = i (1.1 RjC^ f). This indicates a direct relationship between the input current, resistance, capacitance, and frequency of operation.

The filtering component of the circuit consists of a resistor (RL) with a resistance of 100 kΩ and a capacitor (C) of 1 µF. This RC filter is designed to smooth out the output current, ensuring that any high-frequency noise is attenuated. As a result, the ripple voltage at the output is maintained below 10 mV peak, which is critical for applications requiring precision and stability in the output signal.

However, the circuit exhibits a slow response time, characterized by a time constant of 0.1 seconds. This indicates that the circuit will take this duration to respond to changes in the input signal. Furthermore, the settling time of 0.7 seconds to reach within 0.1% of the final value suggests that while the circuit is stable, it may not be suitable for applications requiring rapid response times. Overall, this design balances filtering and stability, making it appropriate for specific applications where precision is paramount, but speed is not the primary concern.In these applications, a pulse input at % is differentiated by a C-R network and the negative-going edge at pin 6 causes the input comparator to trigger the timer circuit. Just as with a V-to-F converter, the average current flowing out of pin 1 is IaverAGE = i (1.1 RjC^ f.

In this simple circuit, this current is filtered in the network RL = 100 k ohm and 1 µF. The ripple will be less than 10 mV peak, but the response will be slow, with a 0.1 second time constant, and settling of 0.7 second to 0.1%