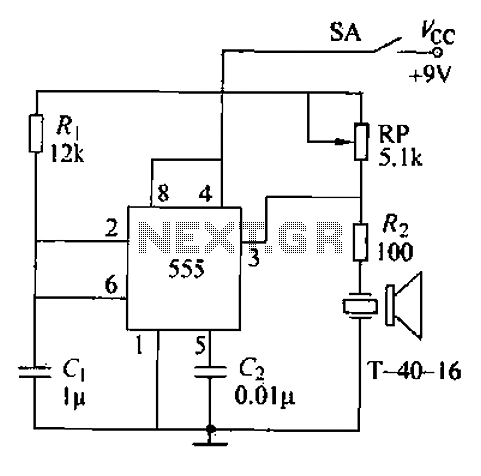

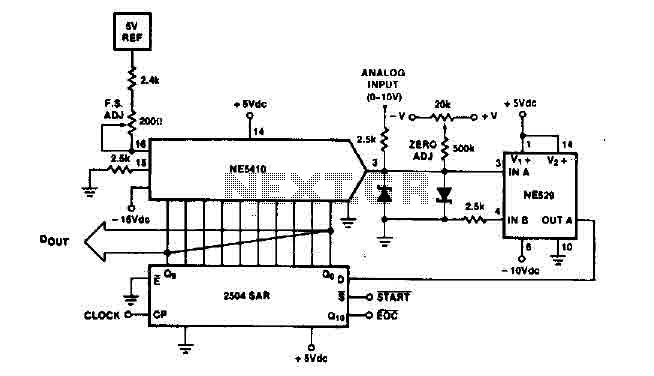

Generating a Delayed Pulse Using The 555 Timer circuit

The circuit below demonstrates the generation of a single positive pulse that is delayed in relation to the trigger input time. It is similar to a previously described circuit but utilizes two stages, allowing for control over both the pulse width and the delay. When the button is pressed, the output of the first stage rises and remains close to the supply voltage until the delay time, which is approximately 1 second, has passed. The second 555 stage does not respond to the rising voltage because it requires a negative, falling voltage at pin 2; therefore, the output of the second stage remains low, and the relay stays de-energized. Once the delay time has elapsed, the output of the first stage drops to a low level, and the falling voltage triggers the second stage to initiate its output cycle, which also lasts about 1 second. This circuit can alternatively be constructed using the dual 555 timer, the 556, although the pin configurations will differ.

The circuit employs two 555 timer ICs configured in monostable mode to achieve the desired pulse generation and delay. The first 555 timer is triggered by a momentary push-button switch, which, when pressed, causes the output to transition high, activating the relay. The output remains high for a predetermined duration, set by an external resistor and capacitor connected to the timing pins of the first 555 timer. This timing component determines the length of the delay before the output transitions back to low.

Once the output of the first timer returns to low after the delay, this falling edge is fed into the trigger pin of the second 555 timer. The second timer is also configured in monostable mode, and it is designed to produce a pulse of a specified width. Its timing components (resistor and capacitor) set the duration of this pulse. The output of the second timer, which drives the relay, remains high for the duration of this pulse, allowing the relay to energize briefly before returning to a de-energized state.

The integration of two stages provides flexibility in controlling both the delay and the pulse width, making this circuit suitable for applications requiring precise timing sequences. The use of a dual 555 timer (556) can simplify the circuit design, reducing the number of components needed while maintaining the same functionality. However, care must be taken to reference the correct pin configurations when using the 556 timer, as they differ from the standard 555 timer layout.The circuit below illustrates generating a single positive pulse which is delayed relative to the trigger input time. The circuit is similar to the one above but employs two stages so that both the pulse width and delay can be controlled.

When the button is depressed, the output of the first stage will move up and remain near the supply voltage un til the delay time has elapsed, which in this case is about 1 second. The second 555 stage will not respond to the rising voltage since it requires a negative, falling voltage at pin 2, and so the second stage output remains low and the relay remains de-energized. At the end of the delay time, the output of the first stage returns to a low level, and the falling voltage causes the second stage to begin it`s output cycle which is also about 1 second as shown.

This same circuit can be built using the dual 555 timer which is a 556, however the pin numbers will be different. 🔗 External reference

The circuit employs two 555 timer ICs configured in monostable mode to achieve the desired pulse generation and delay. The first 555 timer is triggered by a momentary push-button switch, which, when pressed, causes the output to transition high, activating the relay. The output remains high for a predetermined duration, set by an external resistor and capacitor connected to the timing pins of the first 555 timer. This timing component determines the length of the delay before the output transitions back to low.

Once the output of the first timer returns to low after the delay, this falling edge is fed into the trigger pin of the second 555 timer. The second timer is also configured in monostable mode, and it is designed to produce a pulse of a specified width. Its timing components (resistor and capacitor) set the duration of this pulse. The output of the second timer, which drives the relay, remains high for the duration of this pulse, allowing the relay to energize briefly before returning to a de-energized state.

The integration of two stages provides flexibility in controlling both the delay and the pulse width, making this circuit suitable for applications requiring precise timing sequences. The use of a dual 555 timer (556) can simplify the circuit design, reducing the number of components needed while maintaining the same functionality. However, care must be taken to reference the correct pin configurations when using the 556 timer, as they differ from the standard 555 timer layout.The circuit below illustrates generating a single positive pulse which is delayed relative to the trigger input time. The circuit is similar to the one above but employs two stages so that both the pulse width and delay can be controlled.

When the button is depressed, the output of the first stage will move up and remain near the supply voltage un til the delay time has elapsed, which in this case is about 1 second. The second 555 stage will not respond to the rising voltage since it requires a negative, falling voltage at pin 2, and so the second stage output remains low and the relay remains de-energized. At the end of the delay time, the output of the first stage returns to a low level, and the falling voltage causes the second stage to begin it`s output cycle which is also about 1 second as shown.

This same circuit can be built using the dual 555 timer which is a 556, however the pin numbers will be different. 🔗 External reference