Klee Sequencer Circuit Theory of Operation

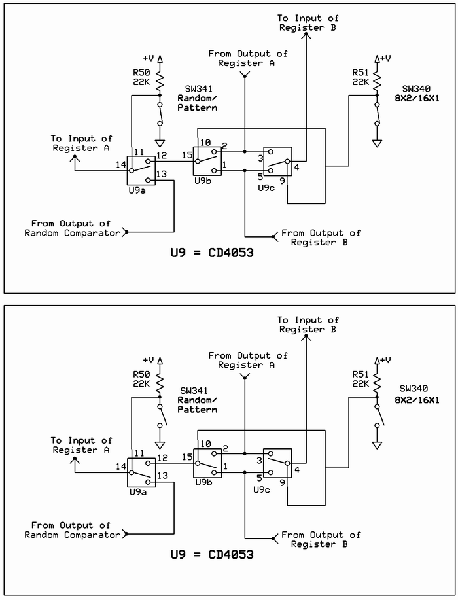

The circuit involves Clock and Load functions, with the Load function being described first. The component U5, a CD4013, is responsible for executing the load function by determining whether the shift register integrated circuits (ICs) operate in parallel or serial mode. For the majority of the time, approximately 99.99%, the shift registers function in serial mode. In this mode, bits cycle through the register from left to right. With each clock pulse, the bit present on the serial input of the shift register enters the register, while the bit in the eighth position exits the register. In parallel mode, each shift register examines the bits configured on its parallel inputs, which are set by pattern switches. The transition to and from parallel mode occurs rapidly, as this mode only examines the programmed bit pattern long enough to load the data before reverting to serial mode. U5 generates two control signals for the shift registers. When the PSA signal goes high, the shift registers switch to serial mode. Following this, the R Async signal goes high. The rising edge of R Async clocks the parallel data into the shift registers. Shortly after, R Async returns to low, which causes PSA to go low, switching the shift registers back to serial mode. The CD4013 manages these operations, triggered by the rising edge of a pulse applied to the clock pin of its first stage (pin 3). Three events can trigger this: the rising edge of the signal at U5, pin 3, clocks the first section's Q signal (pin 1) high, which pulls the PSA signal high. When PSA is high, the two shift register ICs enter parallel mode. The transition of PSA from low to high clocks the second stage of U5 since this signal is also connected to the clock input of the second section (pin 11). Clocking the second section results in its Q signal going high (pin 13), generating a sharp rising pulse that pulls the R Async signal high. The transition of R Async from low to high clocks the parallel data into the shift register ICs. When R Async goes high (Q of the second section), this signal is squared by R22/D3 and slightly delayed by C9. Once it reaches a sufficient level, this signal resets the second section of U5, as it is fed into the reset pin (pin 10). Resetting the second section brings the Q output of the second section low, causing R Async to go low again. This transition briefly pulls the voltage of pull-up resistor R20 low through C18, which in turn causes the output of U2, pin 8, to generate a positive pulse. This pulse is applied to the reset pin of the first section of U5 (pin 4), pulling PSA low and returning the shift registers to serial mode. U5 is then prepared to repeat the operation upon receiving the next load pulse. Manual Load Switch: Pressing the manual load switch pulls R27 low, which briefly lowers the voltage of R18 through C11, the debounce capacitor. When R27 is pulled low, it also pulls pin 5 of U2 low, causing pin 6 of U2 to go high. This signal is ORed by U3 (pin 2) with any pulse that may be generated by the external load input on pin 1 of U3. The output from this section of U3 is applied to pin 8 of U3, where it is ORed with any Gate Bus 1 signal present on pin 9 of U3, and the resultant signal is passed from pin 10 of U3 to the clock input of the first section of U5 (pin 3). External Load Input: Signals applied to the external load input.

The circuit design integrates a CD4013 dual D-type flip-flop to manage the loading and clocking operations of the shift registers. The CD4013’s first section is pivotal in toggling between serial and parallel modes, dictated by the PSA signal. In serial mode, the shift registers sequentially process incoming data, while in parallel mode, they capture multiple bits simultaneously based on the configuration from external switches.

The R Async signal serves a critical role in synchronizing the loading process. The timing of R Async is crucial as it determines when data is latched into the shift registers, ensuring that transitions occur cleanly without data loss. The use of capacitors C9 and C18 introduces necessary delays and stabilization in the signal transitions, preventing unintended glitches that could disrupt the operation.

The manual load switch provides an alternative means to initiate the load function, enhancing the circuit's flexibility. The debounce capacitor C11 ensures that mechanical noise from the switch does not cause multiple spurious triggers, thus maintaining signal integrity.

In summary, this circuit efficiently manages data loading and processing through well-timed control signals, allowing for seamless operation between parallel and serial modes. The design is robust, leveraging common components to achieve functionality that is both reliable and adaptable to various input signals.Clock and Load functions, with Load being the first function described. U5, CD4013, performs the load function by controlling whether the shift register ICs are in the parallel or serial mode. For 99. 99% of the time, the shift registers are in the serial mode. In the serial mode, each shift register will cycle bits through the register, left to right. With each clock pulse, the bit present on the serial input of the shift register will enter the shift register, and the bit present in the eighth position of the shift register will pass out of the shift register. In the parallel mode, each shift register will "look at" the bits programmed on its parallel inputs. The pattern switches set these bits. The switch to and from the parallel mode is a very fast operation - this mode looks at the bit pattern programmed by the pattern switches only long enough to load the data, then the shift registers revert back to serial mode.

Two shift register control signals are generated by U5. When the PSA signal goes high, it puts the shift registers in the serial mode. Immediately afterwards, the R Async signal goes high. When R Async goes high, it clocks the parallel data into the shift registers on its rising edge. Nearly as soon as it goes high, R Async goes low, which in turn causes PSA to go low, which puts the shift registers back in serial mode. The CD4013 calls these shots, and it is told to do so by the rising edge of a pulse applied to the clock pin of its first stage (pin 3).

There are three events that can produce this triggering event: The rising edge of the signal applied to U5, pin 3, clocks the first section`s Q signal (pin 1) high. This pulls the PSA signal high. When PSA is high, the two shift register ICs are put into the parallel mode. When PSA ("Q" pin 1 of U5) transitions from low to high, the rising edge of this signal clocks the second stage of U5, because this signal is also connected to the clock input of the second section (pin 11).

Clocking the second section of U5 causes its Q signal to go high (pin 13). This creates a sharp rising pulse, which pulls the signal R Async high. The transition of R Async from low to high clocks the parallel data into the shift register ICs. When R Async goes high (Q of the second section), this signal is squared up by R22/D3 and slightly delayed by C9. When it pulls high enough, this signal resets the second section of U5, because it is fed into the reset pin (pin 10).

Resetting the second section brings Q of the second section low, causing R Async to go low again. This transition also briefly pulls the voltage of pull-up resistor R20 low through C18. When this signal goes low, it causes the output of U2, Pin 8 to create a positive going pulse. This pulse is applied to the reset pin of the first section of U5 (pin 4), which pulls PSA low, placing the shift registers back into the serial mode. U5 is then ready to complete the operation again whenever the next load pulse is received. Manual Load Switch: When the manual load switch is pressed, R27 is pulled low, which causes the voltage of R18 to pull low briefly through through C11, the "debounce" capacitor.

When R27 is pulled low, it pulls pin 5 of U2 low, which causes pin 6 of U2 to snap high. This signal is ORed by U3 (pin 2) with any pulse that may be generated by the external load input, which would be present on pin 1 of U3. The output of this section of U3 is applied to pin 8 of U3, where it is ORed with any Gate Bus 1 signal that may be present on pin 9 of U3, and the signal is passed from pin 10 of U3 to the clock input of the first section of U5 (pin 3).

External Load Input: Signals applied to the external load input fi 🔗 External reference

The circuit design integrates a CD4013 dual D-type flip-flop to manage the loading and clocking operations of the shift registers. The CD4013’s first section is pivotal in toggling between serial and parallel modes, dictated by the PSA signal. In serial mode, the shift registers sequentially process incoming data, while in parallel mode, they capture multiple bits simultaneously based on the configuration from external switches.

The R Async signal serves a critical role in synchronizing the loading process. The timing of R Async is crucial as it determines when data is latched into the shift registers, ensuring that transitions occur cleanly without data loss. The use of capacitors C9 and C18 introduces necessary delays and stabilization in the signal transitions, preventing unintended glitches that could disrupt the operation.

The manual load switch provides an alternative means to initiate the load function, enhancing the circuit's flexibility. The debounce capacitor C11 ensures that mechanical noise from the switch does not cause multiple spurious triggers, thus maintaining signal integrity.

In summary, this circuit efficiently manages data loading and processing through well-timed control signals, allowing for seamless operation between parallel and serial modes. The design is robust, leveraging common components to achieve functionality that is both reliable and adaptable to various input signals.Clock and Load functions, with Load being the first function described. U5, CD4013, performs the load function by controlling whether the shift register ICs are in the parallel or serial mode. For 99. 99% of the time, the shift registers are in the serial mode. In the serial mode, each shift register will cycle bits through the register, left to right. With each clock pulse, the bit present on the serial input of the shift register will enter the shift register, and the bit present in the eighth position of the shift register will pass out of the shift register. In the parallel mode, each shift register will "look at" the bits programmed on its parallel inputs. The pattern switches set these bits. The switch to and from the parallel mode is a very fast operation - this mode looks at the bit pattern programmed by the pattern switches only long enough to load the data, then the shift registers revert back to serial mode.

Two shift register control signals are generated by U5. When the PSA signal goes high, it puts the shift registers in the serial mode. Immediately afterwards, the R Async signal goes high. When R Async goes high, it clocks the parallel data into the shift registers on its rising edge. Nearly as soon as it goes high, R Async goes low, which in turn causes PSA to go low, which puts the shift registers back in serial mode. The CD4013 calls these shots, and it is told to do so by the rising edge of a pulse applied to the clock pin of its first stage (pin 3).

There are three events that can produce this triggering event: The rising edge of the signal applied to U5, pin 3, clocks the first section`s Q signal (pin 1) high. This pulls the PSA signal high. When PSA is high, the two shift register ICs are put into the parallel mode. When PSA ("Q" pin 1 of U5) transitions from low to high, the rising edge of this signal clocks the second stage of U5, because this signal is also connected to the clock input of the second section (pin 11).

Clocking the second section of U5 causes its Q signal to go high (pin 13). This creates a sharp rising pulse, which pulls the signal R Async high. The transition of R Async from low to high clocks the parallel data into the shift register ICs. When R Async goes high (Q of the second section), this signal is squared up by R22/D3 and slightly delayed by C9. When it pulls high enough, this signal resets the second section of U5, because it is fed into the reset pin (pin 10).

Resetting the second section brings Q of the second section low, causing R Async to go low again. This transition also briefly pulls the voltage of pull-up resistor R20 low through C18. When this signal goes low, it causes the output of U2, Pin 8 to create a positive going pulse. This pulse is applied to the reset pin of the first section of U5 (pin 4), which pulls PSA low, placing the shift registers back into the serial mode. U5 is then ready to complete the operation again whenever the next load pulse is received. Manual Load Switch: When the manual load switch is pressed, R27 is pulled low, which causes the voltage of R18 to pull low briefly through through C11, the "debounce" capacitor.

When R27 is pulled low, it pulls pin 5 of U2 low, which causes pin 6 of U2 to snap high. This signal is ORed by U3 (pin 2) with any pulse that may be generated by the external load input, which would be present on pin 1 of U3. The output of this section of U3 is applied to pin 8 of U3, where it is ORed with any Gate Bus 1 signal that may be present on pin 9 of U3, and the signal is passed from pin 10 of U3 to the clock input of the first section of U5 (pin 3).

External Load Input: Signals applied to the external load input fi 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713