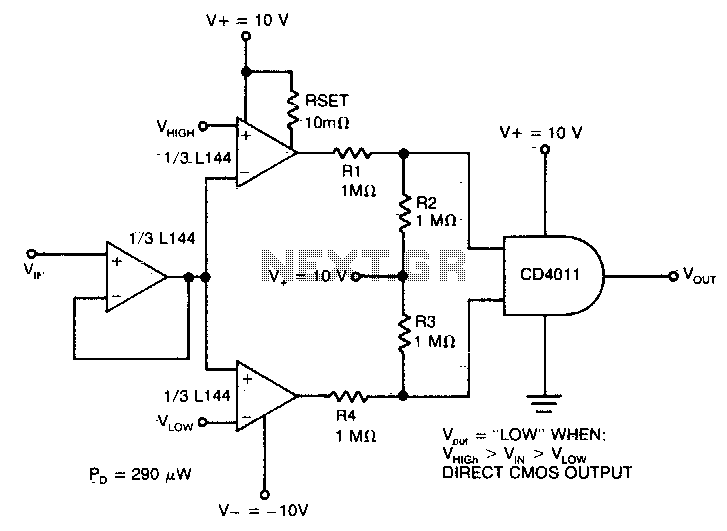

Micropower double ended limit detector

The detector utilizes three sections of an L144 and a DC4011 type CMOS NAND gate to create a very low power voltage monitor. If the input voltage, Vin, is above Vhigh or below Vlow, the output will be a logical high. The output will be low only when the input is within the specified limits.

The circuit employs four 1 megohm resistors, R1, R2, R3, and R4, which serve to convert the bipolar ±10V swing of the operational amplifiers to a 0 to 5V swing that is compatible with ground-referenced CMOS logic.

The primary function of this voltage monitor is to provide a reliable indication of whether the input voltage is within the predefined thresholds. The L144 sections act as voltage comparators, monitoring the input voltage against the set limits, Vhigh and Vlow. When Vin exceeds Vhigh, or falls below Vlow, the output of the NAND gate transitions to a logical high state, signaling that the monitored voltage is outside the acceptable range. Conversely, when Vin is within the specified limits, the output remains low.

The choice of using a CMOS NAND gate is significant due to its low power consumption characteristics, making it suitable for battery-operated devices or applications where power efficiency is critical. The resistors R1 through R4 play a crucial role in ensuring that the analog signals from the operational amplifiers are scaled down appropriately to avoid damage to the CMOS logic and to ensure accurate logical interpretation.

In summary, this voltage monitor circuit effectively combines the functionality of operational amplifiers and CMOS logic to provide a robust solution for monitoring voltage levels in various electronic applications, ensuring that the output accurately reflects the input voltage conditions.The detector uses three sections of an L144 and a DC4011 type CMOS NAND gate to make a very low power voltage monitor. If the input voltage, Vin, is above Vhigh or below Vlow, the output will be a logical high. If (and only if) the input is between the limits will the output be low

The circuit employs four 1 megohm resistors, R1, R2, R3, and R4, which serve to convert the bipolar ±10V swing of the operational amplifiers to a 0 to 5V swing that is compatible with ground-referenced CMOS logic.

The primary function of this voltage monitor is to provide a reliable indication of whether the input voltage is within the predefined thresholds. The L144 sections act as voltage comparators, monitoring the input voltage against the set limits, Vhigh and Vlow. When Vin exceeds Vhigh, or falls below Vlow, the output of the NAND gate transitions to a logical high state, signaling that the monitored voltage is outside the acceptable range. Conversely, when Vin is within the specified limits, the output remains low.

The choice of using a CMOS NAND gate is significant due to its low power consumption characteristics, making it suitable for battery-operated devices or applications where power efficiency is critical. The resistors R1 through R4 play a crucial role in ensuring that the analog signals from the operational amplifiers are scaled down appropriately to avoid damage to the CMOS logic and to ensure accurate logical interpretation.

In summary, this voltage monitor circuit effectively combines the functionality of operational amplifiers and CMOS logic to provide a robust solution for monitoring voltage levels in various electronic applications, ensuring that the output accurately reflects the input voltage conditions.The detector uses three sections of an L144 and a DC4011 type CMOS NAND gate to make a very low power voltage monitor. If the input voltage, Vin, is above Vhigh or below Vlow, the output will be a logical high. If (and only if) the input is between the limits will the output be low

The 1 megohm resistors Rl, R2, R3, and R4 translate the bipolar ±10V swing of the op amps to a 0 to LOV swing acceptable to the ground-referenced CMOS logic.

🔗 External reference