Peak Detector

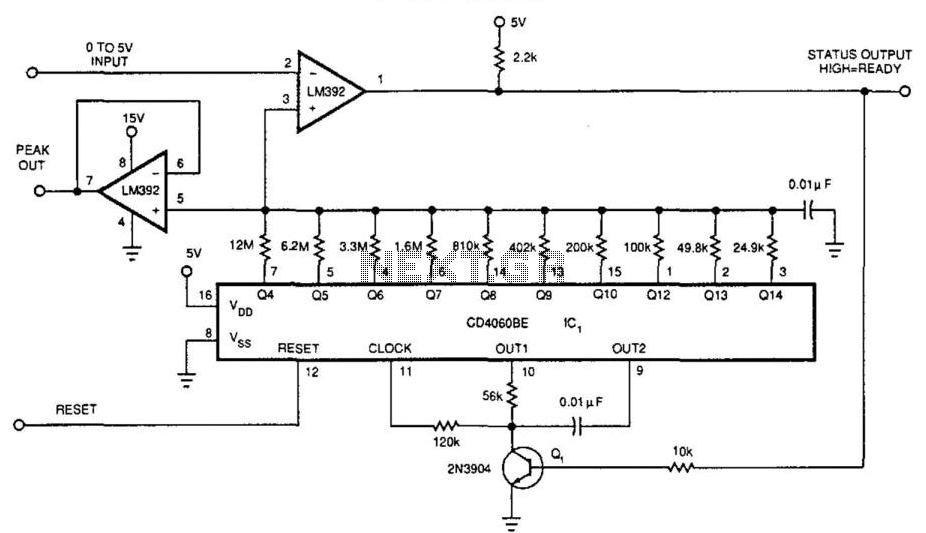

A 0-to-5 V input drives the negative input of the LM392 comparator if the reset (pin 12) of the DC4060BE is pulled high and then low, causing all outputs of ICF1 to be forced low. This action forces the positive input of the comparator to go low. As a result, Q1 is turned off, and the clock oscillator of IC1, operating at approximately 775 Hz, begins counting. The outputs Q4 through Q14 are connected to a ladder configuration. When the counter reaches a count such that the voltage on pin 3 of the LM392 equals the peak input voltage, the counting process halts. This voltage is available at the output of the voltage follower LM392 (pin 7). The maximum time required to acquire a peak is 22 seconds. This circuit is characterized by a slow response time and was originally designed for battery-charging applications.

The circuit utilizes an LM392 comparator, which is a dual comparator with high input impedance and low output impedance, making it suitable for applications requiring voltage comparisons. The design begins with a 0-to-5 V input signal that is applied to the negative input of the LM392. The reset functionality is controlled by pin 12 of the DC4060BE, a binary counter IC. When this pin is pulled high and subsequently low, it resets the counter and forces the outputs of the integrated circuit ICF1 to a low state. This action results in the positive input of the LM392 also being driven low, which is critical for initiating the counting process.

With Q1 turned off, the clock oscillator of IC1, which operates at approximately 775 Hz, begins its counting sequence. The outputs from Q4 to Q14 of the binary counter are configured in a ladder arrangement, which allows for a gradual increase in voltage corresponding to the count value. As the counter progresses, it continues to increment until the voltage at pin 3 of the LM392 matches the peak voltage of the input signal. At this point, the counting process is halted, effectively capturing the peak voltage.

The output voltage, which represents the peak input voltage, is available at pin 7 of the LM392, configured as a voltage follower. This configuration ensures that the output voltage is buffered, providing a stable output that can be used in further processing or monitoring applications. The circuit's design allows for a maximum peak acquisition time of 22 seconds, indicating a relatively slow response time that is appropriate for battery-charging applications where gradual voltage changes are expected and rapid response is not critical.

Overall, this circuit exemplifies a simple yet effective method for peak voltage detection and is well-suited for applications where monitoring of input voltage levels is necessary over extended periods. A 0-to-5 V input drives the negative input of LM392 comparator if reset (pin 12) if DC4060BE is pulled high then low, all out puts of ICF1 are forced low, forcing + input of comparator to go low. Q1 is cut off and ICl"s clock oscillator, running at about 775 Hz, starts counting. The Q4 through Q14 outputs connect to a ladder. When the counter reaches a count so that the voltage on pin 3 of the LM392 equals the peak input voltage, the counter stops. This voltage is available at the output of the voltage follower LM392 (pin 7). The maximum time to acquire a peak is 22 seconds. This circuit is slow and was originally intended for battery-charging applications.

The circuit utilizes an LM392 comparator, which is a dual comparator with high input impedance and low output impedance, making it suitable for applications requiring voltage comparisons. The design begins with a 0-to-5 V input signal that is applied to the negative input of the LM392. The reset functionality is controlled by pin 12 of the DC4060BE, a binary counter IC. When this pin is pulled high and subsequently low, it resets the counter and forces the outputs of the integrated circuit ICF1 to a low state. This action results in the positive input of the LM392 also being driven low, which is critical for initiating the counting process.

With Q1 turned off, the clock oscillator of IC1, which operates at approximately 775 Hz, begins its counting sequence. The outputs from Q4 to Q14 of the binary counter are configured in a ladder arrangement, which allows for a gradual increase in voltage corresponding to the count value. As the counter progresses, it continues to increment until the voltage at pin 3 of the LM392 matches the peak voltage of the input signal. At this point, the counting process is halted, effectively capturing the peak voltage.

The output voltage, which represents the peak input voltage, is available at pin 7 of the LM392, configured as a voltage follower. This configuration ensures that the output voltage is buffered, providing a stable output that can be used in further processing or monitoring applications. The circuit's design allows for a maximum peak acquisition time of 22 seconds, indicating a relatively slow response time that is appropriate for battery-charging applications where gradual voltage changes are expected and rapid response is not critical.

Overall, this circuit exemplifies a simple yet effective method for peak voltage detection and is well-suited for applications where monitoring of input voltage levels is necessary over extended periods. A 0-to-5 V input drives the negative input of LM392 comparator if reset (pin 12) if DC4060BE is pulled high then low, all out puts of ICF1 are forced low, forcing + input of comparator to go low. Q1 is cut off and ICl"s clock oscillator, running at about 775 Hz, starts counting. The Q4 through Q14 outputs connect to a ladder. When the counter reaches a count so that the voltage on pin 3 of the LM392 equals the peak input voltage, the counter stops. This voltage is available at the output of the voltage follower LM392 (pin 7). The maximum time to acquire a peak is 22 seconds. This circuit is slow and was originally intended for battery-charging applications.