Prepping Residential Gateways for WAN Access

Much of the focus on residential gateway designs has been on distributing communication connectivity within a home. However, to effectively distribute content, gateways must first possess a reliable WAN interface that provides access to cable modems, fixed broadband wireless, or DSL broadband connections. This article will examine some of the design challenges engineers encounter when developing the WAN portion of a residential gateway. Specifically, it will address the difficulties of integrating an ADSL modem/router into a gateway without compromising ADSL signal performance. The interface to the ADSL line consists of a set of discrete circuits and an ADSL chipset. Typically, the analog chip, known as the analog front end (AFE), encompasses all necessary analog-to-digital conversion, digital-to-analog conversion, and filtering functions required to generate and acquire the discrete multi-tone (DMT) signal. In many ADSL modem designs, the receive side (Rx) of the AFE first filters the DMT signal from the line using a plain old telephone system (POTS) high-pass (HP) filter to attenuate speech and POTS signaling. This approach also prevents ADSL signals from leaking into the POTS bandwidth. A channel filter is employed to reduce echo signals, thereby enhancing the characteristics of the Rx path, specifically the maximum allowable useful amplitude within the chip. The signal is amplified by a low-noise gain stage (ranging from -15 to +31 dB) and subsequently filtered using a low-pass filter to avoid anti-aliasing and facilitate further digital processing by removing unwanted high-frequency, out-of-band noise. A 13-bit analog-to-digital (ADC) converter samples the data at 8.832 Mbps, converts the signal into a digital format, and transmits it to the DMT signal processor via a digital interface. On the transmission side (Tx) of the AFE, the 12-bit data stream at 8.832 Mbps from the DMT signal processor, through the digital interface, is transformed by a digital-to-analog converter (DAC) into an analog signal. This signal is then filtered to reduce DMT sidelobe levels and comply with the transmitter spectral response specified by the American National Standards Institute (ANSI). This filter stage also minimizes out-of-band noise, which could echo back to the Rx path, to an acceptable level. The pre-driver buffers the signal for the external line driver and can control the level of attenuation (between -9 and +6 dB) for short loops before the signal reaches the line driver. In the United States, a band-pass filter must be utilized between the AFE and the line. The high-pass component of this filter (Fc=30 kHz) ensures that no ADSL signals leak into the POTS band, while the low-pass filter (Fc=125 kHz) prevents the Tx signal from interfering with the Rx band and overloading the Rx stage. The AFE often includes circuitry to support the voltage-controlled crystal oscillator (VCXO), which serves as a slave to the clock on the central office side. The VCXO, the receive path circuitry, board layout, and component selection are critical factors when designing an ADSL WAN subsystem capable of supporting long-reach performance up to 12 km. These elements significantly influence noise suppression, ensuring optimal performance in the ADSL modem. The ADSL modem on the customer premises equipment (CPE) extracts the clock to synchronize with the central office, employing a clock recovery scheme using a discrete VCXO. For the VCXO function, designers may choose off-the-shelf solutions; however, this can be costly, leading many companies to construct a VCXO circuit from discrete components as a more economical alternative. It is crucial to ensure that no noise generated within the VCXO propagates, which can be achieved using an inductor/capacitor configuration.

The design of a residential gateway with an integrated ADSL modem/router necessitates careful consideration of the WAN interface to ensure optimal performance and reliability. The AFE plays a pivotal role in this architecture, handling the critical tasks of signal conditioning and conversion. The integration of high-pass and low-pass filters is essential to maintain signal integrity by preventing interference between the ADSL and POTS signals. The use of a VCXO for clock recovery is also vital, as it synchronizes the modem with the central office, ensuring stable data transmission.

Engineers must also focus on the layout of the PCB to minimize noise coupling between components, which can significantly affect performance. The selection of components, particularly those in the Rx and Tx paths, should prioritize low noise and high linearity to maximize the effective range of the ADSL connection. Additionally, the design must accommodate various environmental factors, such as temperature variations, which can influence the performance of analog components.

In summary, the development of a residential gateway with ADSL capabilities involves a complex interplay of analog and digital technologies, requiring meticulous attention to detail in both the design and implementation phases to achieve a robust and efficient communication solution.Much of the focus around residential gateways designs has focused on distributing communication connectivity within a home or residence. But, in order to distribute content, gateways must first have an effective WAN interface that provides access to cable modem, fixed broadband wireless, or DSL broadband pipes.

In this article, we`ll explore someof the design challenges that engineers will face when building the WAN portion of a residential gateway design. Specifically, we`ll look at the challenges of building an ADSL modem/router into a gateway without jeopardizing the performance of the ADSL signals. The interface to the ADSL line is composed of a set of discrete circuits as well as an ADSL chip set.

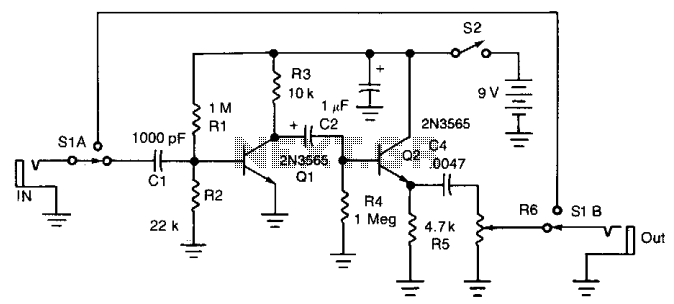

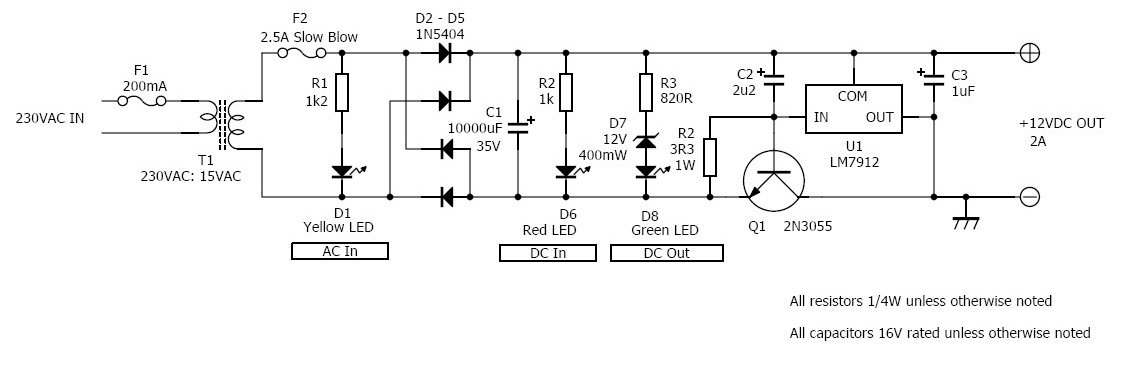

In general, the analog chip, termed the analog front end (AFE) [See Figure 1], incorporates all the analog-to-digital conversion, digital-to-analog conversion, and filtering functions required to acquire and create the characteristic discrete multi-tone (DMT) signal. For many ADSL modem designs, the receive side (Rx) of the AFE will first filter the DMT signal coming from the line to the AFE chip using a plain old telephone system (POTS) high-pass (HP) filter for attenuation of speech and POTS signaling.

This method also prevents the ADSL signal from leaking into the POTS bandwidth. A channel filter is also used for attenuation of the echo signal to improve the characteristics of the Rx path, or the maximum amount of useful amplitude allowed within the chip. The signal is amplified by a low noise gain stage (-15 to +31 dB) and is follow by a low-pass signal that is filtered to avoid anti-aliasing and to ease further digital processing by removing unwanted high-frequency, out-of-band noise.

A 13-bit analog-to-digital (ADC) converter samples the data at 8. 832 Mbps, transforms the signal into a digital representation, and sends it to the DMT signal processor via the digital interface. On the transmission side (Tx) of the AFE, the 12-bit data stream at 8. 832 Mbps coming from the DMT signal processor, through the digital interface, is transformed by a digital-to-analog converter (DAC) into an analog signal.

This signal is then filtered to decrease DMT sidelobe levels and meet the transmitter spectral response outlined in the American National Standards Institute (ANSI) specifications. This filter stage also reduces the out-of-band noise, which can be echoed to the Rx path, to an acceptable level.

The pre-driver buffers the signal for the external line driver and, for short loops, can control the level of attenuation (between -9 and +6 dB) before the signal reaches the line driver. In the United States, a band-pass filter must be used between the AFE and the line. The high-pass part of this filter (Fc=30 kHz) ensures that no ADSL signals leak in the POTS band. The low-pass filter (Fc=125 kHz) keeps the Tx signal from interfering in the Rx band and overloading the Rx stage.

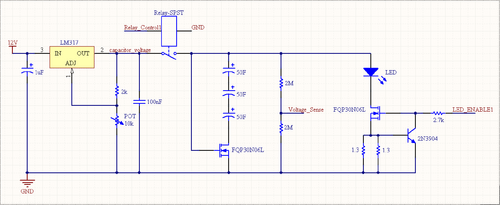

The AFE often includes the circuitry to support the voltage-controlled crystal oscillator (VCXO), which acts as a slave to the clock on the central office side. The VCXO, the receive path circuitry, board layout, and component selection are the three most important factors when creating an ADSL WAN subsystem that can support long-reach performance up to 12 km.

These three factors play a dominant role in suppressing noise to ensure the best performance in the ADSL modem. Let`s first take a look at the requirements for the VCXO circuitry. The ADSL modem on the CPE extracts the clock to synchronize the central office and the CPE —basically a clock recovery scheme using a discrete VCXO.

For the VCXO function, the designer can select an off-the-shelf solution. However, as this approach is expensive, most companies construct a VCXO circuit from discrete devices for a cost-effective alternative. An important note: to ensure no noise present within the VCXO is spread, the designer can use an inductor/capacit

🔗 External reference

The design of a residential gateway with an integrated ADSL modem/router necessitates careful consideration of the WAN interface to ensure optimal performance and reliability. The AFE plays a pivotal role in this architecture, handling the critical tasks of signal conditioning and conversion. The integration of high-pass and low-pass filters is essential to maintain signal integrity by preventing interference between the ADSL and POTS signals. The use of a VCXO for clock recovery is also vital, as it synchronizes the modem with the central office, ensuring stable data transmission.

Engineers must also focus on the layout of the PCB to minimize noise coupling between components, which can significantly affect performance. The selection of components, particularly those in the Rx and Tx paths, should prioritize low noise and high linearity to maximize the effective range of the ADSL connection. Additionally, the design must accommodate various environmental factors, such as temperature variations, which can influence the performance of analog components.

In summary, the development of a residential gateway with ADSL capabilities involves a complex interplay of analog and digital technologies, requiring meticulous attention to detail in both the design and implementation phases to achieve a robust and efficient communication solution.Much of the focus around residential gateways designs has focused on distributing communication connectivity within a home or residence. But, in order to distribute content, gateways must first have an effective WAN interface that provides access to cable modem, fixed broadband wireless, or DSL broadband pipes.

In this article, we`ll explore someof the design challenges that engineers will face when building the WAN portion of a residential gateway design. Specifically, we`ll look at the challenges of building an ADSL modem/router into a gateway without jeopardizing the performance of the ADSL signals. The interface to the ADSL line is composed of a set of discrete circuits as well as an ADSL chip set.

In general, the analog chip, termed the analog front end (AFE) [See Figure 1], incorporates all the analog-to-digital conversion, digital-to-analog conversion, and filtering functions required to acquire and create the characteristic discrete multi-tone (DMT) signal. For many ADSL modem designs, the receive side (Rx) of the AFE will first filter the DMT signal coming from the line to the AFE chip using a plain old telephone system (POTS) high-pass (HP) filter for attenuation of speech and POTS signaling.

This method also prevents the ADSL signal from leaking into the POTS bandwidth. A channel filter is also used for attenuation of the echo signal to improve the characteristics of the Rx path, or the maximum amount of useful amplitude allowed within the chip. The signal is amplified by a low noise gain stage (-15 to +31 dB) and is follow by a low-pass signal that is filtered to avoid anti-aliasing and to ease further digital processing by removing unwanted high-frequency, out-of-band noise.

A 13-bit analog-to-digital (ADC) converter samples the data at 8. 832 Mbps, transforms the signal into a digital representation, and sends it to the DMT signal processor via the digital interface. On the transmission side (Tx) of the AFE, the 12-bit data stream at 8. 832 Mbps coming from the DMT signal processor, through the digital interface, is transformed by a digital-to-analog converter (DAC) into an analog signal.

This signal is then filtered to decrease DMT sidelobe levels and meet the transmitter spectral response outlined in the American National Standards Institute (ANSI) specifications. This filter stage also reduces the out-of-band noise, which can be echoed to the Rx path, to an acceptable level.

The pre-driver buffers the signal for the external line driver and, for short loops, can control the level of attenuation (between -9 and +6 dB) before the signal reaches the line driver. In the United States, a band-pass filter must be used between the AFE and the line. The high-pass part of this filter (Fc=30 kHz) ensures that no ADSL signals leak in the POTS band. The low-pass filter (Fc=125 kHz) keeps the Tx signal from interfering in the Rx band and overloading the Rx stage.

The AFE often includes the circuitry to support the voltage-controlled crystal oscillator (VCXO), which acts as a slave to the clock on the central office side. The VCXO, the receive path circuitry, board layout, and component selection are the three most important factors when creating an ADSL WAN subsystem that can support long-reach performance up to 12 km.

These three factors play a dominant role in suppressing noise to ensure the best performance in the ADSL modem. Let`s first take a look at the requirements for the VCXO circuitry. The ADSL modem on the CPE extracts the clock to synchronize the central office and the CPE —basically a clock recovery scheme using a discrete VCXO.

For the VCXO function, the designer can select an off-the-shelf solution. However, as this approach is expensive, most companies construct a VCXO circuit from discrete devices for a cost-effective alternative. An important note: to ensure no noise present within the VCXO is spread, the designer can use an inductor/capacit

🔗 External reference