SPDIF Monitor Circuit

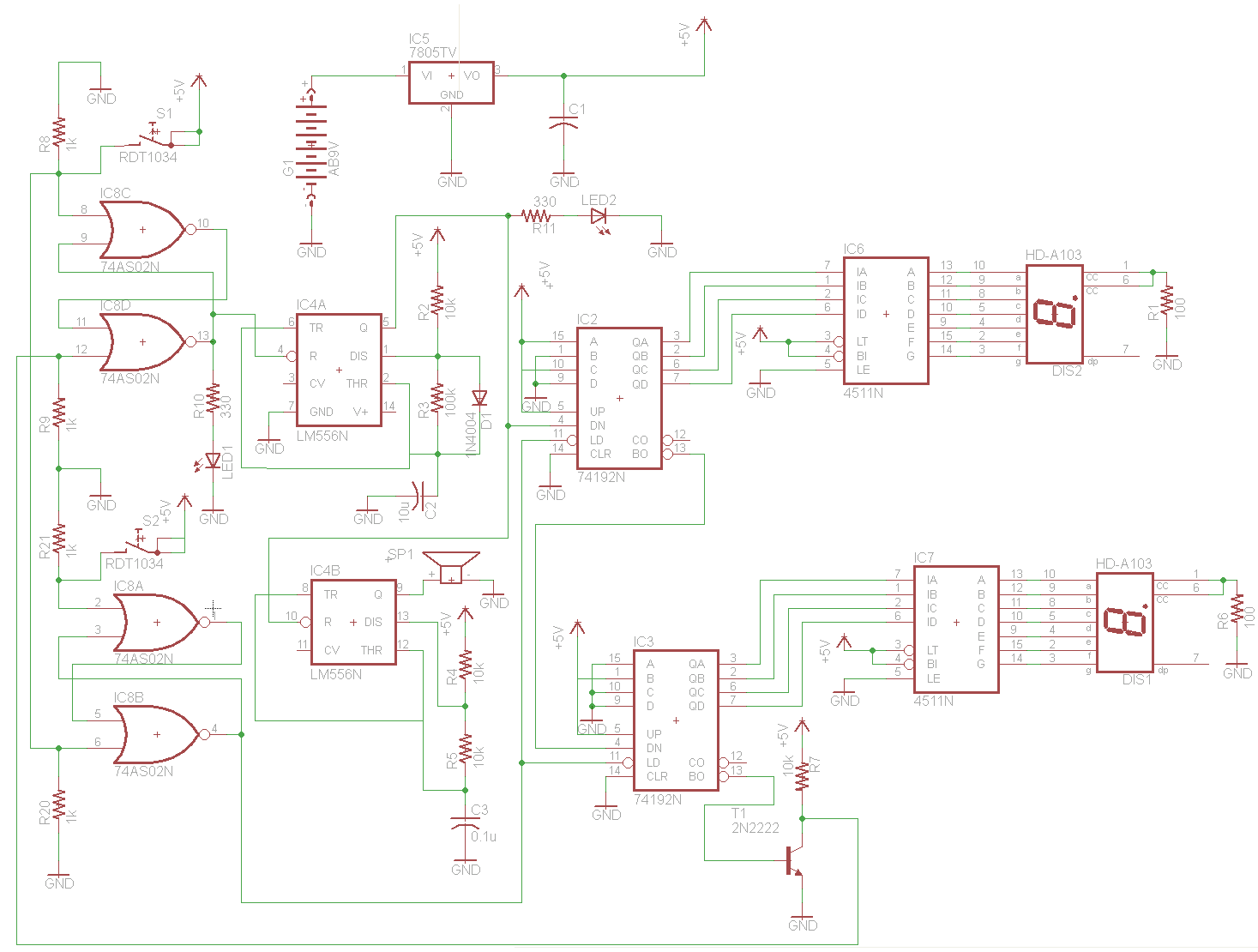

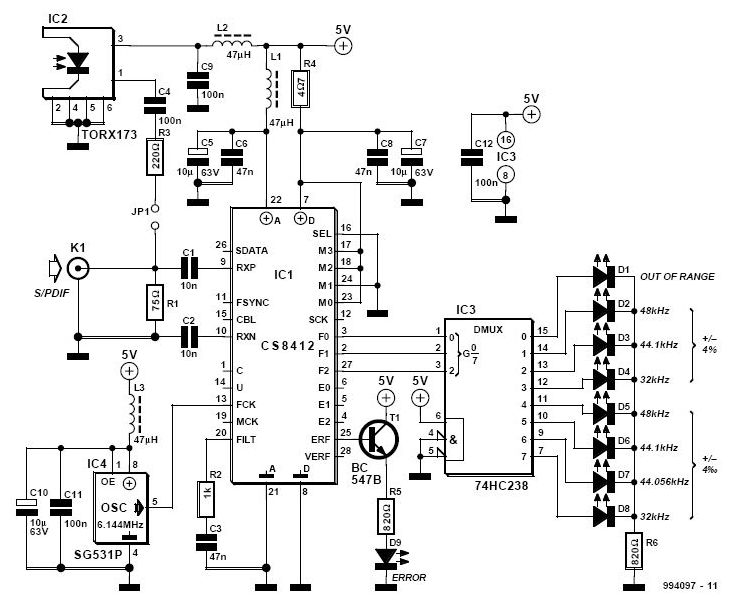

The S/PDIF monitor is an application of the digital audio interface receiver Type CS8412 from Crystal. Previous articles have covered the decoding of S/PDIF (Sony/Philips Digital Interface Format) into data, bit clock, and L/R clock for use in devices such as digital voltmeters or clipping indicators. The integration of an external reference oscillator, IC4, allows the receiver to distinguish incoming signals using a frequency comparator. The monitor indicates differences in frequency from a reference value in three distinct ways. The precision of these limits is determined by the accuracy of the crystal oscillator; the SG531P crystal from Epson used in this design has an accuracy of ±100 ppm. The optical input provided by IC2 enhances functionality. The output from this circuit is directed across R1 via C4, R3, and jumper JP1. The voltage across R1 can serve as a digital output, requiring adjustments to the value of R3 as necessary. Additionally, the circuit can function as a relay station or for jitter reduction. For these applications, IC1 is configured in a special mode (mode 13) when M3 is set to 1, and M0, M2 are set to 1, 0, and 1, respectively. With these settings, the received S/PDIF data, including the preamble, is transmitted directly to the output. The bit clock, SCK, then operates at twice the frequency compared to coded data. A TOSLINK module or a coaxial output can be connected via a buffer, such as multiple parallel-linked 74HC04 inverters, to the SDATA output. A demultiplexer, specifically a 3-to-8 line decoder IC3, decodes the data at F0 to F2 into eight separate light-emitting diodes. Diode D9 indicates when IC1 is receiving no data or poor-quality data. The entire circuit operates with a maximum current draw of 35 mA.

The S/PDIF monitor circuit utilizes the CS8412 receiver to facilitate the reception and decoding of digital audio signals. The CS8412 is a versatile component that supports various digital audio formats, making it suitable for applications in audio processing and monitoring. The inclusion of an external reference oscillator (IC4) enhances the circuit's ability to accurately compare incoming signal frequencies against a stable reference, thereby improving the overall performance of the monitor.

The optical input provided by IC2 is a critical feature that allows for the reception of digital audio signals via optical fiber, a common method for transmitting high-quality audio. The output configuration involving R1, C4, R3, and jumper JP1 is designed to allow flexibility in how the output voltage is utilized, which can be essential for interfacing with different types of digital systems.

The circuit's ability to function as a relay station or jitter reducer is particularly valuable in professional audio applications, where signal integrity is paramount. By configuring IC1 in mode 13, the circuit can bypass certain processing steps, allowing for a more direct transfer of the S/PDIF data to the output. This configuration ensures that the bit clock operates at an optimal frequency, which is crucial for maintaining synchronization in digital audio systems.

The addition of a demultiplexer (IC3) to decode the audio data into individual channels for visual indication via light-emitting diodes provides a user-friendly interface for monitoring signal quality. The presence of diode D9 serves as a diagnostic tool, alerting users to potential issues with signal reception. Overall, the S/PDIF monitor circuit is a sophisticated solution for monitoring and processing digital audio signals, with various applications in both consumer and professional audio environments.The SPDIF monitor is one of the many applications possible with the digital audio interface receiver Type CS8412 from Crystal. Other applications described in earlier issues of this magazine dealt with the decoding of the S/PDIF (Sony/Philips Digital Interface Format) into data, bit clock and L/R clock in a digital voltmeter or clipping indicator.

The addition of an external reference oscillator, IC4, enables the receiver to differentiate incoming signals by means of a frequency comparator and this is what the present monitor does. When the frequency of an incoming signal differs from a reference value, the difference is indicated in one of three ways: Clearly, the accuracy of the crystal oscillator determines the precision of these limits (the SG531P crystal from Epson used in the diagram has an accuracy of ±100 ppm).

The optical input provided by IC2 is a useful addition. The output of this circuit is applied across R1 via C4, R3 and jumperJP1. The potential across R1 may also be used as a digital output, in which case the value of R3 needs to be adapted as necessary. The circuit may also be used as a kind of relay station or as a means for reducing jitter. For these purposes, IC1 is connected in a special mode (mode 13) when M3 is made 1, and M0 M2, 1, 0, and 1, respectively.

When these levels are set the received S/PDIF data, including the preamble, is transferred directly to the output. The bit clock, SCK, then has a value twice as high as would be the case with coded data. It is possible to connect a TOSLINK module, or a coaxial output via a buffer (such as a number of parallel-linked 74HC04 inverters), to the SDATA output.

A demultiplexer, that is, 3-to-8 line decoder IC3, is used to decode the data at F0 F2 to eight separate light-emitting diodes. Diode D9 indicates whether IC1 receives no or poor data. The overall circuit draws a current of not more than 35 mA. 🔗 External reference

The S/PDIF monitor circuit utilizes the CS8412 receiver to facilitate the reception and decoding of digital audio signals. The CS8412 is a versatile component that supports various digital audio formats, making it suitable for applications in audio processing and monitoring. The inclusion of an external reference oscillator (IC4) enhances the circuit's ability to accurately compare incoming signal frequencies against a stable reference, thereby improving the overall performance of the monitor.

The optical input provided by IC2 is a critical feature that allows for the reception of digital audio signals via optical fiber, a common method for transmitting high-quality audio. The output configuration involving R1, C4, R3, and jumper JP1 is designed to allow flexibility in how the output voltage is utilized, which can be essential for interfacing with different types of digital systems.

The circuit's ability to function as a relay station or jitter reducer is particularly valuable in professional audio applications, where signal integrity is paramount. By configuring IC1 in mode 13, the circuit can bypass certain processing steps, allowing for a more direct transfer of the S/PDIF data to the output. This configuration ensures that the bit clock operates at an optimal frequency, which is crucial for maintaining synchronization in digital audio systems.

The addition of a demultiplexer (IC3) to decode the audio data into individual channels for visual indication via light-emitting diodes provides a user-friendly interface for monitoring signal quality. The presence of diode D9 serves as a diagnostic tool, alerting users to potential issues with signal reception. Overall, the S/PDIF monitor circuit is a sophisticated solution for monitoring and processing digital audio signals, with various applications in both consumer and professional audio environments.The SPDIF monitor is one of the many applications possible with the digital audio interface receiver Type CS8412 from Crystal. Other applications described in earlier issues of this magazine dealt with the decoding of the S/PDIF (Sony/Philips Digital Interface Format) into data, bit clock and L/R clock in a digital voltmeter or clipping indicator.

The addition of an external reference oscillator, IC4, enables the receiver to differentiate incoming signals by means of a frequency comparator and this is what the present monitor does. When the frequency of an incoming signal differs from a reference value, the difference is indicated in one of three ways: Clearly, the accuracy of the crystal oscillator determines the precision of these limits (the SG531P crystal from Epson used in the diagram has an accuracy of ±100 ppm).

The optical input provided by IC2 is a useful addition. The output of this circuit is applied across R1 via C4, R3 and jumperJP1. The potential across R1 may also be used as a digital output, in which case the value of R3 needs to be adapted as necessary. The circuit may also be used as a kind of relay station or as a means for reducing jitter. For these purposes, IC1 is connected in a special mode (mode 13) when M3 is made 1, and M0 M2, 1, 0, and 1, respectively.

When these levels are set the received S/PDIF data, including the preamble, is transferred directly to the output. The bit clock, SCK, then has a value twice as high as would be the case with coded data. It is possible to connect a TOSLINK module, or a coaxial output via a buffer (such as a number of parallel-linked 74HC04 inverters), to the SDATA output.

A demultiplexer, that is, 3-to-8 line decoder IC3, is used to decode the data at F0 F2 to eight separate light-emitting diodes. Diode D9 indicates whether IC1 receives no or poor data. The overall circuit draws a current of not more than 35 mA. 🔗 External reference