synthesized PLL for Low Power FM transmitter

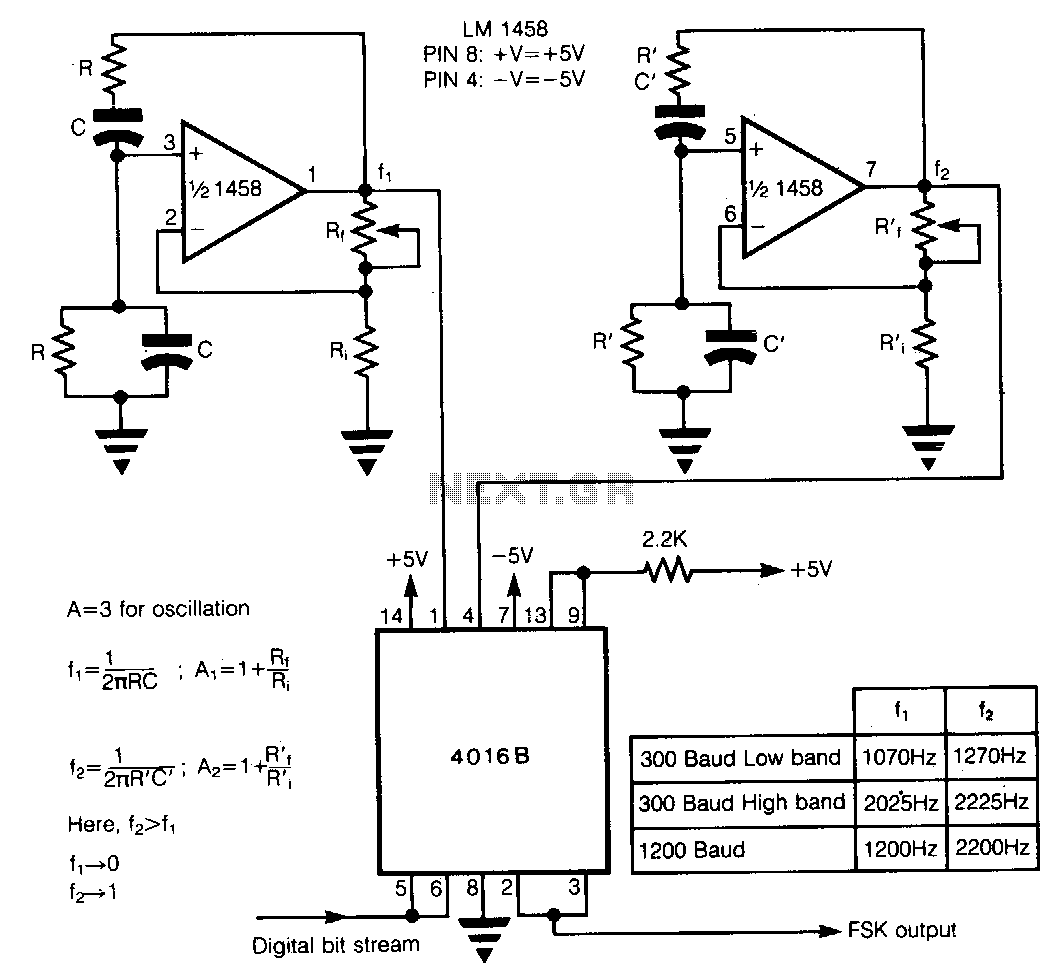

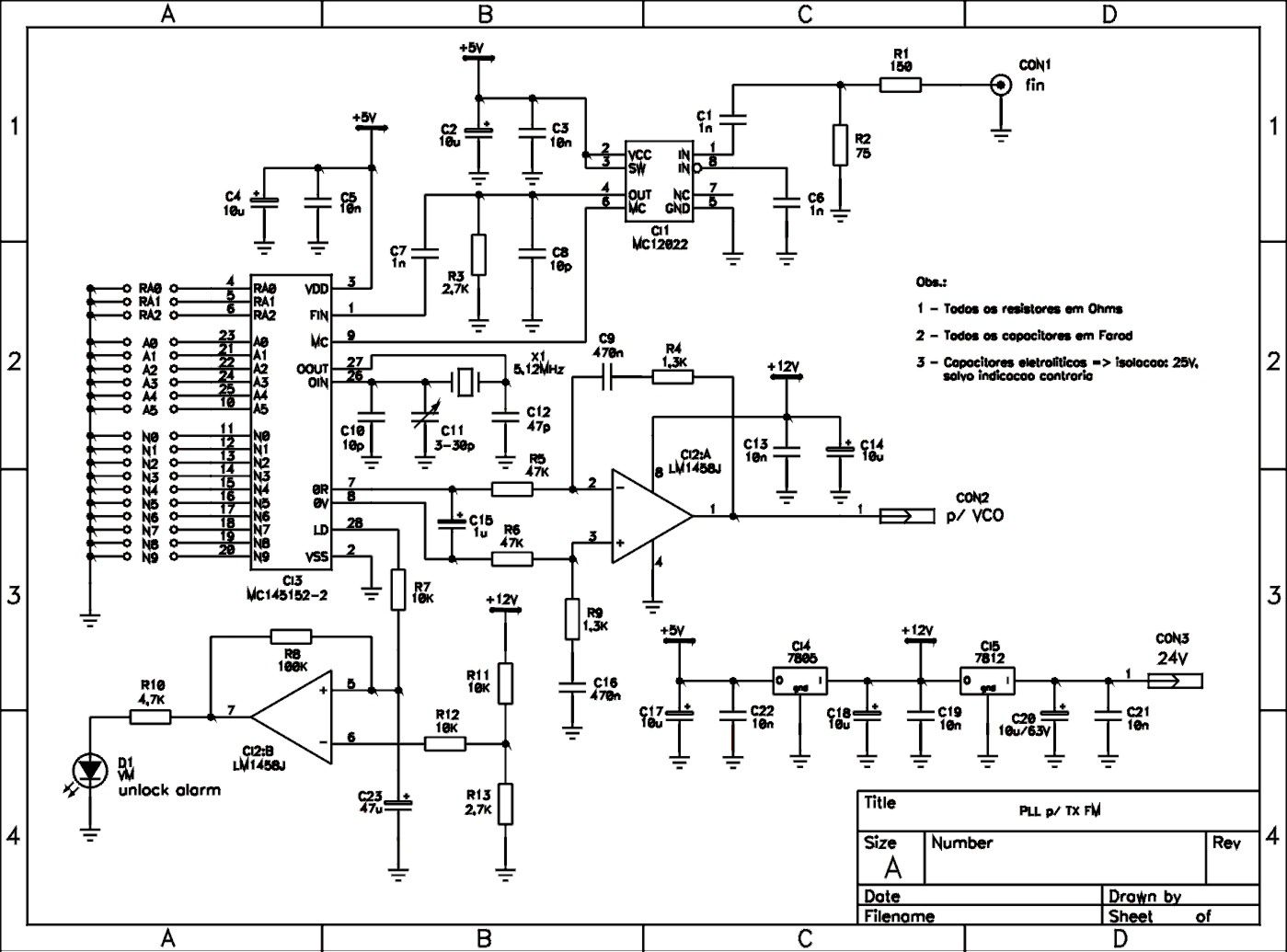

This is a schematic of a synthesized Phase-Locked Loop (PLL) for a low-power FM transmitter. It can also be utilized with other circuits, provided that the loop filter response, components, VCO tank circuit, and appropriate thumbswitch programming keys and crystal values are recalculated. The original FM transmitter project was designed to operate in both synthesized and open-loop free oscillator configurations. The synthesized version ensures high frequency stability and can also lock onto digital FM receivers with a 200 kHz step, which is standard in many countries. A crystal reference of 5.12 MHz was used to achieve 10 kHz steps, which is adequate for FM channeling of 200 kHz. The design also depends on the R divider for the crystal reference; in this case, R=512 was implemented for the MC145151P2 from Motorola. The prescaler divider, denoted as P, is typically set to P=40 for the MC12016. The PLL requires downconversion of the input frequency (pin 1) because the phase/frequency comparator operates effectively at a maximum input frequency of 10 MHz or 15 MHz.

The synthesized PLL circuit is a critical component in low-power FM transmitter designs, allowing for precise frequency control and stability. The architecture generally consists of a voltage-controlled oscillator (VCO), a phase/frequency comparator, and a loop filter. The VCO generates an output frequency that can be adjusted based on the input control voltage. The phase/frequency comparator compares the output frequency of the VCO with a reference frequency derived from the crystal oscillator. The output of the comparator is used to adjust the control voltage applied to the VCO, ensuring that the VCO frequency locks onto the desired frequency.

In this design, the use of a 5.12 MHz crystal reference is essential for achieving the required frequency steps. The selection of the R divider value (R=512) is crucial, as it determines how the reference frequency is scaled down to match the VCO frequency. This allows for finer frequency adjustments and ensures compatibility with the FM channel spacing requirements.

The prescaler (P=40) reduces the input frequency to a manageable level for the PLL, allowing it to function correctly within its specified input frequency range. The downconversion process is necessary because the phase/frequency comparator has a limited operating frequency range. By ensuring that the input frequency does not exceed 10 MHz or 15 MHz, the PLL can maintain accurate phase and frequency comparisons, leading to stable operation.

The flexibility of this PLL design enables it to be adapted for use in various applications beyond low-power FM transmission. By recalibrating the loop filter and VCO components, as well as adjusting the programming keys and crystal values, this circuit can be tailored to meet specific frequency stability and locking requirements for different systems.This is schematic of a synthesized PLL for the Low Power FM transmitter. By the way, you also can use it with other circuits, just pay attention to recalculate the loop filter response and components, VCO tank circuit, and the correct thumbswitch programming keys, crystal value. The original project of FM transmitter was made to operate in both co nfiguration ( synthesized or open loop free oscilattor), with synthesized version you can assure very high frequency stability, and also lock digital FM receivers ( 200KHz step in major of countries). A crystal reference of 5. 12 MHz was employed to assure 10 KHz steps ( enough sufficient to FM channeling of 200 KHz), and it also depends of R divider crystal reference, here I used R=512 to the MC145151P2 of Motorola.

P - is the prescaler divider, normally P=40 to MC12016, the PLL needs downconverter the input frequency ( pin1) because the phase/frequency comparator just work at maximum of 10MHz or 15MHz input frequency. 🔗 External reference

The synthesized PLL circuit is a critical component in low-power FM transmitter designs, allowing for precise frequency control and stability. The architecture generally consists of a voltage-controlled oscillator (VCO), a phase/frequency comparator, and a loop filter. The VCO generates an output frequency that can be adjusted based on the input control voltage. The phase/frequency comparator compares the output frequency of the VCO with a reference frequency derived from the crystal oscillator. The output of the comparator is used to adjust the control voltage applied to the VCO, ensuring that the VCO frequency locks onto the desired frequency.

In this design, the use of a 5.12 MHz crystal reference is essential for achieving the required frequency steps. The selection of the R divider value (R=512) is crucial, as it determines how the reference frequency is scaled down to match the VCO frequency. This allows for finer frequency adjustments and ensures compatibility with the FM channel spacing requirements.

The prescaler (P=40) reduces the input frequency to a manageable level for the PLL, allowing it to function correctly within its specified input frequency range. The downconversion process is necessary because the phase/frequency comparator has a limited operating frequency range. By ensuring that the input frequency does not exceed 10 MHz or 15 MHz, the PLL can maintain accurate phase and frequency comparisons, leading to stable operation.

The flexibility of this PLL design enables it to be adapted for use in various applications beyond low-power FM transmission. By recalibrating the loop filter and VCO components, as well as adjusting the programming keys and crystal values, this circuit can be tailored to meet specific frequency stability and locking requirements for different systems.This is schematic of a synthesized PLL for the Low Power FM transmitter. By the way, you also can use it with other circuits, just pay attention to recalculate the loop filter response and components, VCO tank circuit, and the correct thumbswitch programming keys, crystal value. The original project of FM transmitter was made to operate in both co nfiguration ( synthesized or open loop free oscilattor), with synthesized version you can assure very high frequency stability, and also lock digital FM receivers ( 200KHz step in major of countries). A crystal reference of 5. 12 MHz was employed to assure 10 KHz steps ( enough sufficient to FM channeling of 200 KHz), and it also depends of R divider crystal reference, here I used R=512 to the MC145151P2 of Motorola.

P - is the prescaler divider, normally P=40 to MC12016, the PLL needs downconverter the input frequency ( pin1) because the phase/frequency comparator just work at maximum of 10MHz or 15MHz input frequency. 🔗 External reference