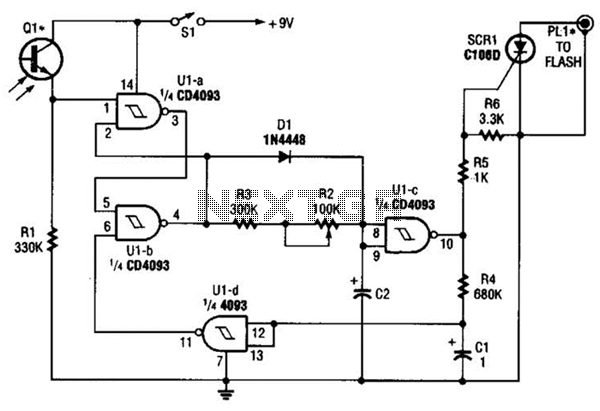

Time Delay Flash Trigger Circuit Circuit

The circuit is built around a single 4093 quad 2-input NAND Schmitt trigger. Two gates from that quad package (U1-a and U1-b) are configured as a set-reset flip-flop.

The 4093 integrated circuit (IC) contains four independent 2-input NAND gates with Schmitt trigger characteristics, which provide a high degree of noise immunity and are suitable for use in digital circuits requiring clean transitions. In this configuration, two of the NAND gates (U1-a and U1-b) are utilized to create a set-reset (SR) flip-flop.

The set-reset flip-flop operates by using the NAND gates to store a binary state. The output of U1-a is connected to one input of U1-b, while the output of U1-b is fed back to one input of U1-a, forming a feedback loop essential for maintaining the state of the flip-flop. The other inputs of both NAND gates are connected to the set (S) and reset (R) control signals. When the set input is activated (logic high), U1-a outputs a logic low, which in turn causes U1-b to output a logic high, thereby setting the flip-flop. Conversely, activating the reset input causes U1-b to output a logic low, which resets the output of U1-a to logic high.

This configuration allows for stable binary storage, where the outputs can remain in their respective states until the set or reset inputs are activated again. The Schmitt trigger action ensures that the transition between high and low states is clean, eliminating any unwanted oscillations or noise that could affect the reliability of the flip-flop operation. This circuit is commonly used in applications requiring memory storage, pulse generation, and state retention in digital systems. The circuit is built around a single 4093 quad 2-input NAND Schmitt trigger. Two gates from that quad package (Ul-a and Ul-b) are configured as a set-reset flip-flop. 🔗 External reference

The 4093 integrated circuit (IC) contains four independent 2-input NAND gates with Schmitt trigger characteristics, which provide a high degree of noise immunity and are suitable for use in digital circuits requiring clean transitions. In this configuration, two of the NAND gates (U1-a and U1-b) are utilized to create a set-reset (SR) flip-flop.

The set-reset flip-flop operates by using the NAND gates to store a binary state. The output of U1-a is connected to one input of U1-b, while the output of U1-b is fed back to one input of U1-a, forming a feedback loop essential for maintaining the state of the flip-flop. The other inputs of both NAND gates are connected to the set (S) and reset (R) control signals. When the set input is activated (logic high), U1-a outputs a logic low, which in turn causes U1-b to output a logic high, thereby setting the flip-flop. Conversely, activating the reset input causes U1-b to output a logic low, which resets the output of U1-a to logic high.

This configuration allows for stable binary storage, where the outputs can remain in their respective states until the set or reset inputs are activated again. The Schmitt trigger action ensures that the transition between high and low states is clean, eliminating any unwanted oscillations or noise that could affect the reliability of the flip-flop operation. This circuit is commonly used in applications requiring memory storage, pulse generation, and state retention in digital systems. The circuit is built around a single 4093 quad 2-input NAND Schmitt trigger. Two gates from that quad package (Ul-a and Ul-b) are configured as a set-reset flip-flop. 🔗 External reference