Video Digitizer Project

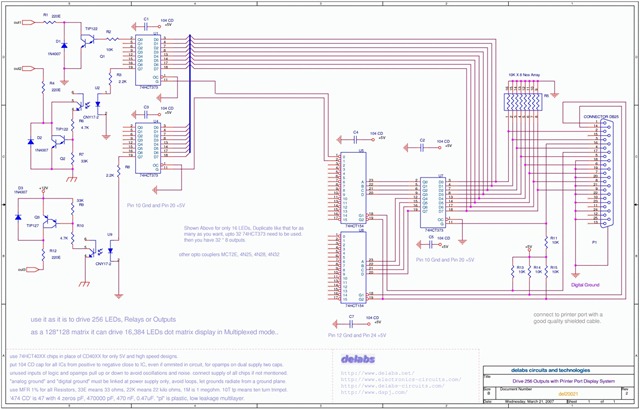

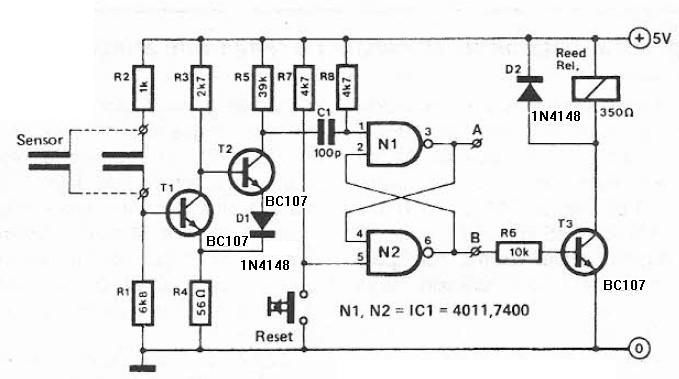

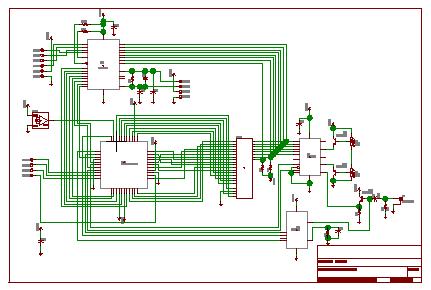

This is the original Circuit Cellar ImageWise Transmitter that was initially used. The code was disassembled to capture two half-size images, allowing for the extraction of images from both the odd and even fields. Code was then written to subtract the two fields, resulting in an image of the laser beam. The video line was scanned to determine the location of the maximum pixel intensity, yielding 128 values, each representing a specific range. A version was desired that was not copyrighted and not dependent on a processor. Therefore, a breadboard version was created using TTL logic. It should be noted that there is an 8751 CPU on the board. The original design was perceived to have an excessive number of components. Additionally, to experiment with the Xilinx starter package, a CPLD was developed to replace all the logic chips. The XC9536 CPLD substituted for 10 TTL logic chips. It is important to mention that this version included a 68HC11 daughterboard, which is not visible in the accompanying photo.

The described circuit involves a modification of the Circuit Cellar ImageWise Transmitter, which is primarily focused on image processing through the manipulation of video fields. The disassembly of the original code facilitated the capture of two half-size images—one from the odd field and one from the even field. The subsequent subtraction of these fields is a critical process that isolates the laser beam's image, enabling precise analysis of pixel intensity.

In the design, the scanning of the video line to determine the maximum pixel intensity is essential for generating a set of 128 values. Each of these values corresponds to a specific intensity range, providing a detailed representation of the laser beam's characteristics. The goal of creating a non-copyrighted, processor-independent version prompted the transition to a breadboard implementation utilizing TTL (Transistor-Transistor Logic) components. The inclusion of the 8751 CPU indicates a level of complexity in processing capabilities despite the desire for a simplified design.

The recognition of an excessive number of components led to the exploration of a more efficient solution using a Complex Programmable Logic Device (CPLD). The XC9536 CPLD was chosen for its ability to replace multiple TTL logic chips—specifically, ten in this case—thus streamlining the circuit and reducing its footprint. The integration of the 68HC11 daughterboard further enhances the functionality of the design, although it is not depicted in the accompanying visuals.

Overall, this circuit represents a sophisticated approach to image processing and analysis, leveraging both traditional TTL logic and modern CPLD technology to achieve a compact and efficient design suitable for various applications in the field of electronics.This is the original Circuit Cellar ImageWise Transmitter that I started with. I disassembled the code and made it grab two half size images. This allowed me to get an image from the odd field and even field. I then wrote code to subtract the two fields which left me with the image of the laser beam. Then it scanned the video line to return the lo cation of the max pixel intensity. So I ended up with 128 values. Each value represents a range. I wanted a version which was not copyrighted and was not processor dependent. So I breadboarded this version using TTL logic. (Note: there is an 8751 CPU on the board. ) I thought I had way to many parts. I also wanted to try out my Xilinx starter package. So I created a CPLD which replaces all the logic chips. The XC9536 CPLD replaced 10 TTL logic chips. (Note: This version had a 68HC11 daughter board. Which isn`t present in the photo. ) 🔗 External reference

The described circuit involves a modification of the Circuit Cellar ImageWise Transmitter, which is primarily focused on image processing through the manipulation of video fields. The disassembly of the original code facilitated the capture of two half-size images—one from the odd field and one from the even field. The subsequent subtraction of these fields is a critical process that isolates the laser beam's image, enabling precise analysis of pixel intensity.

In the design, the scanning of the video line to determine the maximum pixel intensity is essential for generating a set of 128 values. Each of these values corresponds to a specific intensity range, providing a detailed representation of the laser beam's characteristics. The goal of creating a non-copyrighted, processor-independent version prompted the transition to a breadboard implementation utilizing TTL (Transistor-Transistor Logic) components. The inclusion of the 8751 CPU indicates a level of complexity in processing capabilities despite the desire for a simplified design.

The recognition of an excessive number of components led to the exploration of a more efficient solution using a Complex Programmable Logic Device (CPLD). The XC9536 CPLD was chosen for its ability to replace multiple TTL logic chips—specifically, ten in this case—thus streamlining the circuit and reducing its footprint. The integration of the 68HC11 daughterboard further enhances the functionality of the design, although it is not depicted in the accompanying visuals.

Overall, this circuit represents a sophisticated approach to image processing and analysis, leveraging both traditional TTL logic and modern CPLD technology to achieve a compact and efficient design suitable for various applications in the field of electronics.This is the original Circuit Cellar ImageWise Transmitter that I started with. I disassembled the code and made it grab two half size images. This allowed me to get an image from the odd field and even field. I then wrote code to subtract the two fields which left me with the image of the laser beam. Then it scanned the video line to return the lo cation of the max pixel intensity. So I ended up with 128 values. Each value represents a range. I wanted a version which was not copyrighted and was not processor dependent. So I breadboarded this version using TTL logic. (Note: there is an 8751 CPU on the board. ) I thought I had way to many parts. I also wanted to try out my Xilinx starter package. So I created a CPLD which replaces all the logic chips. The XC9536 CPLD replaced 10 TTL logic chips. (Note: This version had a 68HC11 daughter board. Which isn`t present in the photo. ) 🔗 External reference