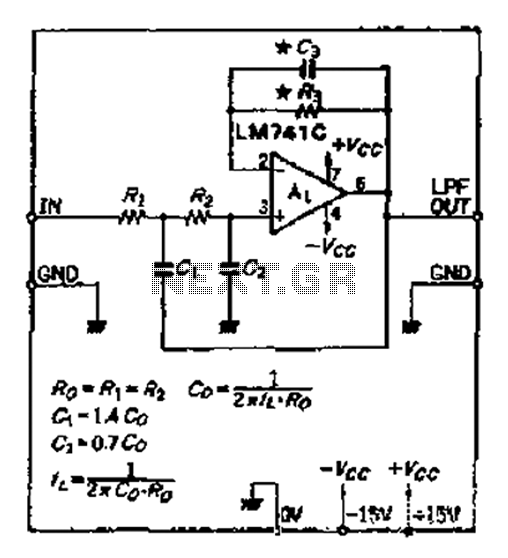

12dB-oct by the OP amplifiers low-pass filter

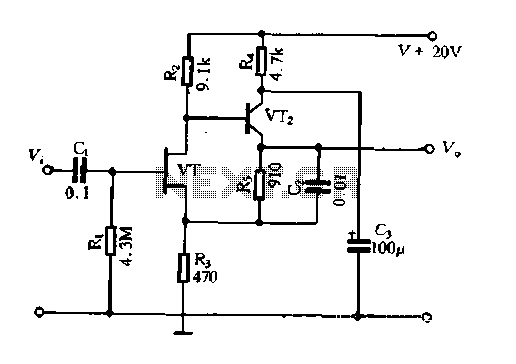

A 12dB/oct Butterworth filter circuit is designed to achieve a flat frequency response. The optimal value for the circuit's Q factor is 0.707, which ensures a flat characteristic. The feedback capacitance must be selected to maintain high capacity and reach a predetermined quality factor (Q) based on the mouth/mouth iTC,/2 formula. To achieve a Q of 0.707, specific relationships must be established between the circuit components. When calculating the effective parameters, the CI 2 of the mouth/2 must be considered. The cut-off frequency can be selected with some flexibility; however, if the resistance (Ro) is too high, it can introduce input bias offset in the operational amplifier due to speech signal effects. To mitigate this bias current, a feedback loop with an appropriate resistor (R) may be added. If a FET input operational amplifier is utilized, the input bias current will be minimal, typically only a few hundred microamps, which helps to eliminate bias issues. The capacitor C3 is included to suppress voltage spikes, and its capacitance should be selected within the range of 22 µF to a suitable upper limit.

The 12dB/oct Butterworth filter is characterized by its smooth frequency response and minimal ripple in the passband. The design aims to achieve a Q factor of 0.707, which is critical for maintaining the desired flatness of the filter's response. The feedback capacitance plays a pivotal role in establishing the filter's characteristics and must be chosen carefully to ensure that the desired Q value is attained. The relationship between the components in the circuit is crucial; for instance, the feedback capacitance (Cl) and the resistance (R) must be properly calibrated to maintain the integrity of the signal while minimizing distortion.

The cut-off frequency of the filter can be adjusted, providing some design flexibility. However, care must be taken to avoid excessively high resistance values, as this can lead to operational amplifier input bias offsets that may affect performance, particularly in audio applications. The feedback loop is essential for compensating for these biases, and the choice of an FET input operational amplifier can significantly reduce the input bias current, thus enhancing the overall performance of the filter.

Capacitor C3 serves an important function in the circuit by suppressing voltage spikes that could adversely affect the filter's operation. The selection of its capacitance is also critical; a range of 22 µF is suggested, with the upper limit determined by the specific application requirements. Overall, the design of this Butterworth filter circuit requires careful consideration of component values and relationships to achieve the desired performance characteristics.12dB/oct Butterworth second port (most flat characteristic) of the filter circuit value is pregnant shall be 0.707 to get the characteristic flat, and for cl, the feedback capa citance roar should be taken to ensure high-capacity reaches a predetermined opening value oQ value from the mouth/mouth iTC,/2 formula. In order to make the port 0. 707, a. And c soil must be established cl 4QI. I 2aI the mouth broom relationship. When calculating the effective parameters, according to CI 2 of mouth/2 Xiao, workers Island, Port I 1/2 port x2 help, a worker Xiao calculated sampling D, and oyster I5il not vend, this week can mound up checking Q value.

Although the cut-off frequency is selected with a certain degree of freedom, but the resistance Ro is too large, it will generate the OP amplifier input bias offset by the impact of speech, accrual calculation, chu o, analyze whether there is a problem here feedback loop plus R, to offset the input bias current, if the choice of FET input ol) amplifier, the input bias current is very small, only a few hundred microamps spread can to remove chu 3. c3 role is to suppress spikes, the choice of its capacity range of 22 ~ sipFo

The 12dB/oct Butterworth filter is characterized by its smooth frequency response and minimal ripple in the passband. The design aims to achieve a Q factor of 0.707, which is critical for maintaining the desired flatness of the filter's response. The feedback capacitance plays a pivotal role in establishing the filter's characteristics and must be chosen carefully to ensure that the desired Q value is attained. The relationship between the components in the circuit is crucial; for instance, the feedback capacitance (Cl) and the resistance (R) must be properly calibrated to maintain the integrity of the signal while minimizing distortion.

The cut-off frequency of the filter can be adjusted, providing some design flexibility. However, care must be taken to avoid excessively high resistance values, as this can lead to operational amplifier input bias offsets that may affect performance, particularly in audio applications. The feedback loop is essential for compensating for these biases, and the choice of an FET input operational amplifier can significantly reduce the input bias current, thus enhancing the overall performance of the filter.

Capacitor C3 serves an important function in the circuit by suppressing voltage spikes that could adversely affect the filter's operation. The selection of its capacitance is also critical; a range of 22 µF is suggested, with the upper limit determined by the specific application requirements. Overall, the design of this Butterworth filter circuit requires careful consideration of component values and relationships to achieve the desired performance characteristics.12dB/oct Butterworth second port (most flat characteristic) of the filter circuit value is pregnant shall be 0.707 to get the characteristic flat, and for cl, the feedback capa citance roar should be taken to ensure high-capacity reaches a predetermined opening value oQ value from the mouth/mouth iTC,/2 formula. In order to make the port 0. 707, a. And c soil must be established cl 4QI. I 2aI the mouth broom relationship. When calculating the effective parameters, according to CI 2 of mouth/2 Xiao, workers Island, Port I 1/2 port x2 help, a worker Xiao calculated sampling D, and oyster I5il not vend, this week can mound up checking Q value.

Although the cut-off frequency is selected with a certain degree of freedom, but the resistance Ro is too large, it will generate the OP amplifier input bias offset by the impact of speech, accrual calculation, chu o, analyze whether there is a problem here feedback loop plus R, to offset the input bias current, if the choice of FET input ol) amplifier, the input bias current is very small, only a few hundred microamps spread can to remove chu 3. c3 role is to suppress spikes, the choice of its capacity range of 22 ~ sipFo