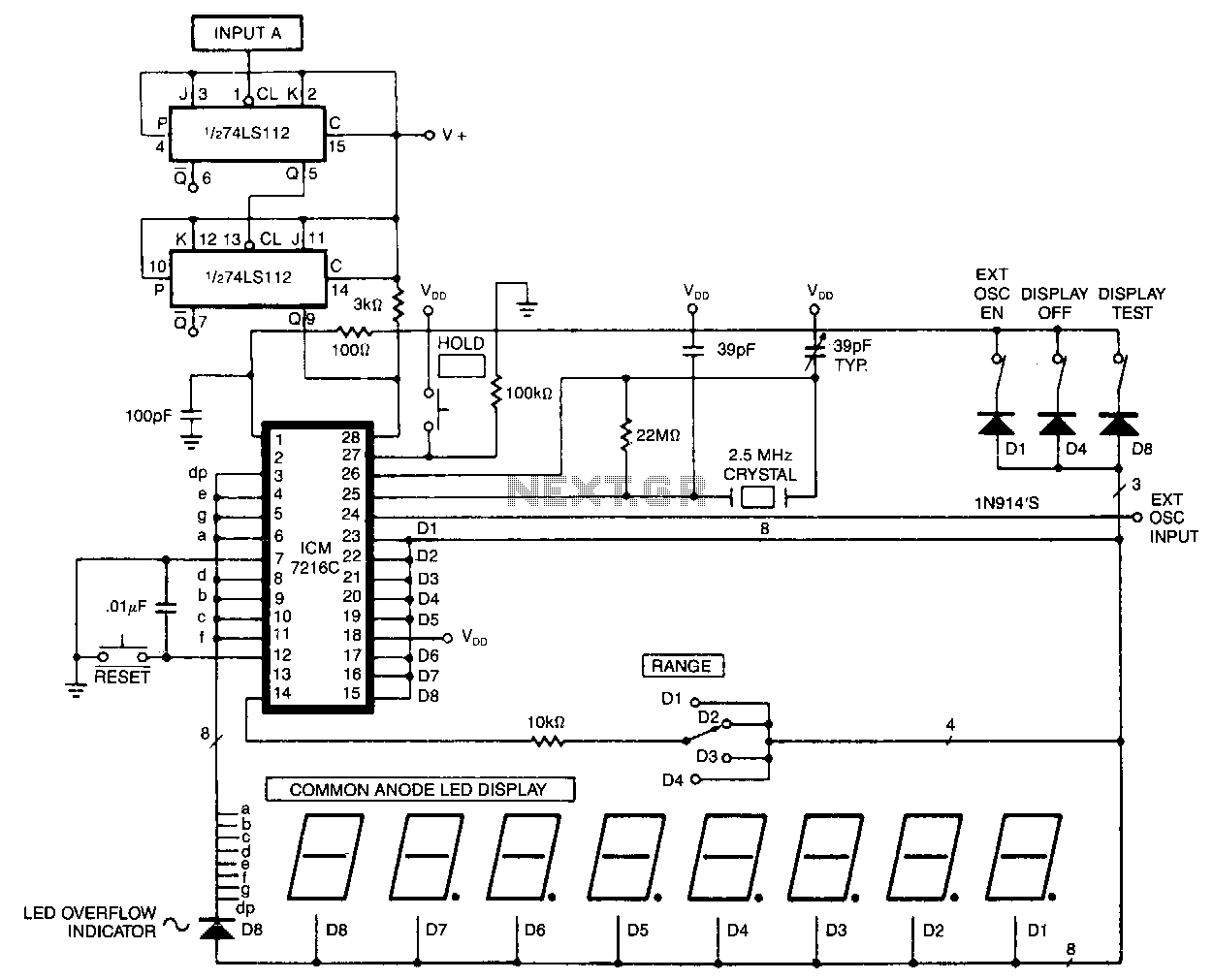

1Hz Timebase For Readout And Counter Applications

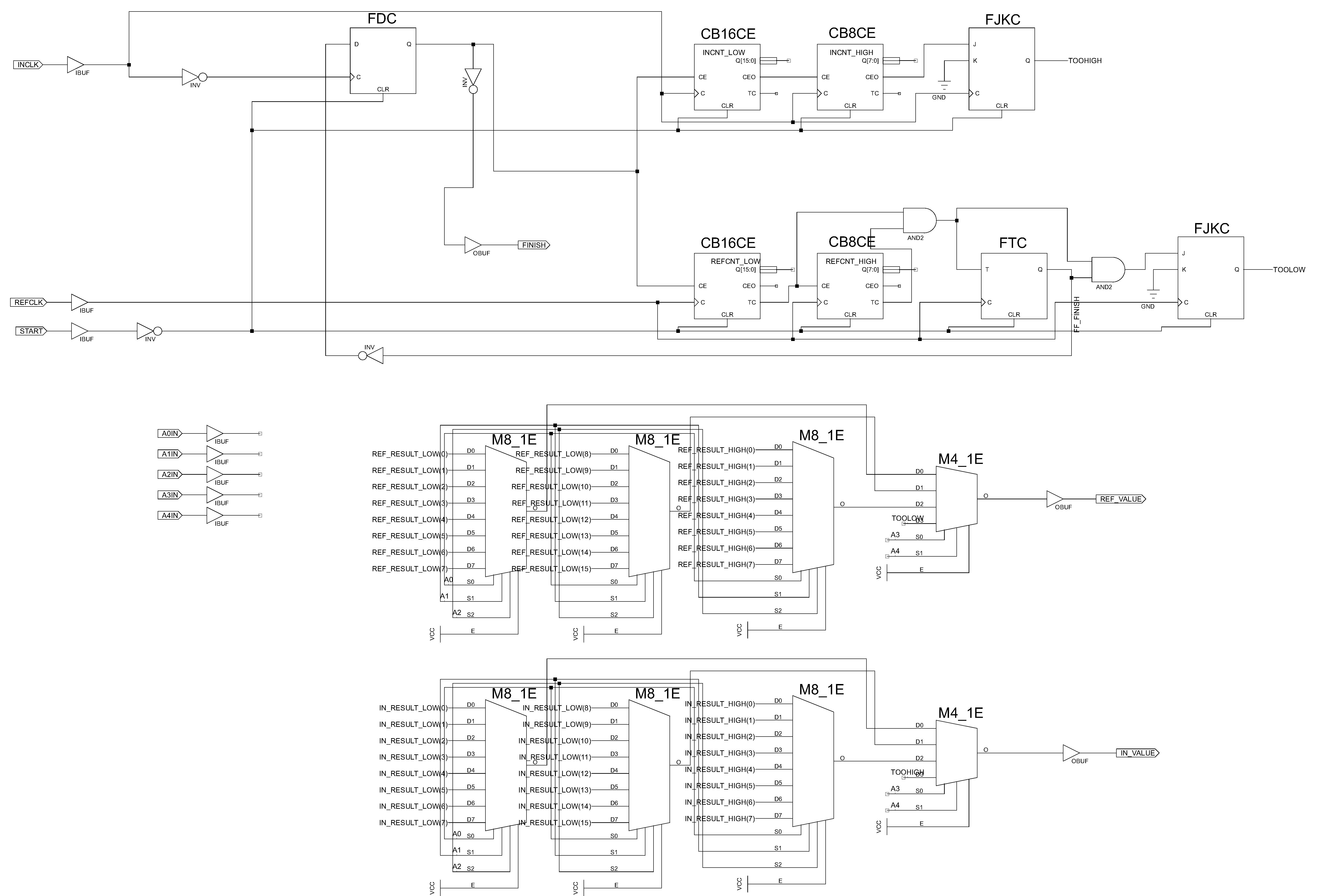

This counter facilitates the direct readout of frequency-generating equipment by incorporating a 1-Hz time base to latch, reset, and condition the count signal. The design allows for the selection of either polarity. By differentiating, inverting, and ORing the clock pulses in XOR gate U2A, a series of 1-Hz, positive, 200-µs pulses is produced. For latching, the 1-Hz stream is further differentiated in U2B, input 1, to generate a 50-µs pulse. Although the output of U2B transitions from high to low, it can be inverted by setting input 2 to low. Since the reset pulse must follow the latch signal, the 1-Hz stream from U2A is delayed by 100 µs at U2C input 1. The output pulse polarity is controlled by adjusting U2C's input 2 to either high or low.

The described counter circuit is an effective tool for frequency measurement and signal processing applications. It utilizes a combination of digital logic gates, specifically XOR gates, to manipulate clock pulses and generate the necessary timing signals for latching and resetting operations. The 1-Hz time base serves as a reliable reference frequency, ensuring accurate counting and timing.

The design's flexibility to select polarity is advantageous in various applications, allowing the user to adapt the circuit to different signal requirements. The differentiation and inversion processes performed by U2A and U2B are critical for generating precise pulse widths, which are essential for reliable latching. The 200-µs and 50-µs pulse widths are tailored for optimal performance in the context of frequency measurement.

The additional delay introduced by U2C ensures that the reset pulse does not interfere with the latching operation, maintaining the integrity of the counting process. The ability to control the output pulse polarity through U2C's input is a significant feature, providing further versatility in output signal characteristics.

Overall, this counter circuit exemplifies a robust design for frequency measurement, integrating essential digital logic components to achieve accurate and flexible operation. It is suitable for applications ranging from laboratory frequency analysis to embedded systems requiring precise timing control. This counter makes direct readout of frequency-generating equipment very easy when a 1-H z time-base is added to latch, reset, and the count signal is conditioned. This design has the flexibility to select either polarity. By differentiating, inverting, and ORing the clock pulses in XOR gate U2A, a stream of 1-Hz, positive, 200-/as pulses is generated. For latching, the 1-Hz stream is again differentiated in U2B, input 1 to supply a 50-/as pulse. Though U2B"s output goes from high to low, it can be reversed, by making input 2 low. Because the reset pulse must occur after the latch signal, the 1-Hz stream from U2A is delayed 100 at U2C input 1.

The output-pulse polarity is determined by making U2C"s input 2 either high or low.

The described counter circuit is an effective tool for frequency measurement and signal processing applications. It utilizes a combination of digital logic gates, specifically XOR gates, to manipulate clock pulses and generate the necessary timing signals for latching and resetting operations. The 1-Hz time base serves as a reliable reference frequency, ensuring accurate counting and timing.

The design's flexibility to select polarity is advantageous in various applications, allowing the user to adapt the circuit to different signal requirements. The differentiation and inversion processes performed by U2A and U2B are critical for generating precise pulse widths, which are essential for reliable latching. The 200-µs and 50-µs pulse widths are tailored for optimal performance in the context of frequency measurement.

The additional delay introduced by U2C ensures that the reset pulse does not interfere with the latching operation, maintaining the integrity of the counting process. The ability to control the output pulse polarity through U2C's input is a significant feature, providing further versatility in output signal characteristics.

Overall, this counter circuit exemplifies a robust design for frequency measurement, integrating essential digital logic components to achieve accurate and flexible operation. It is suitable for applications ranging from laboratory frequency analysis to embedded systems requiring precise timing control. This counter makes direct readout of frequency-generating equipment very easy when a 1-H z time-base is added to latch, reset, and the count signal is conditioned. This design has the flexibility to select either polarity. By differentiating, inverting, and ORing the clock pulses in XOR gate U2A, a stream of 1-Hz, positive, 200-/as pulses is generated. For latching, the 1-Hz stream is again differentiated in U2B, input 1 to supply a 50-/as pulse. Though U2B"s output goes from high to low, it can be reversed, by making input 2 low. Because the reset pulse must occur after the latch signal, the 1-Hz stream from U2A is delayed 100 at U2C input 1.

The output-pulse polarity is determined by making U2C"s input 2 either high or low.