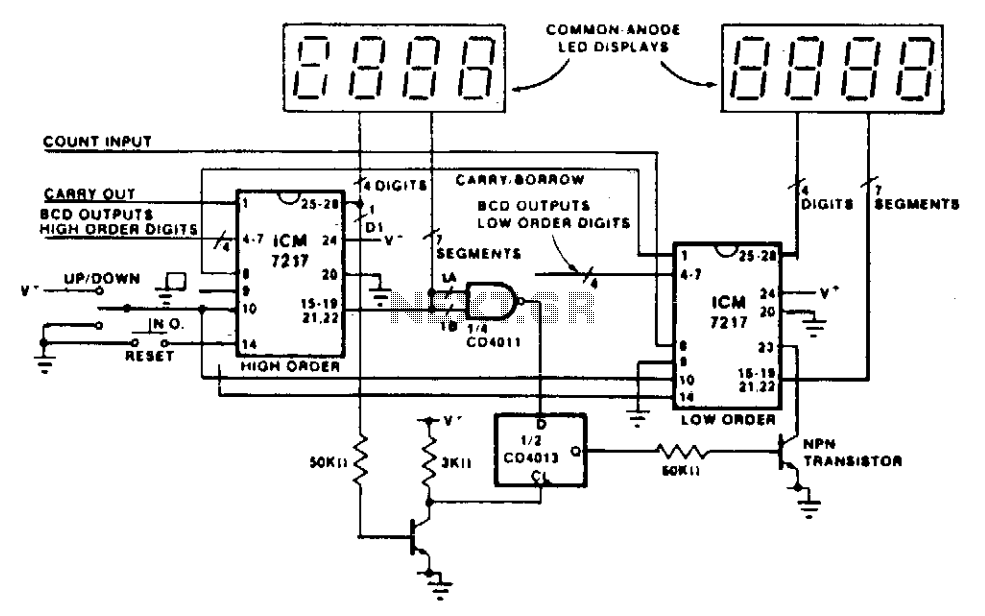

8-Digit up-down counter

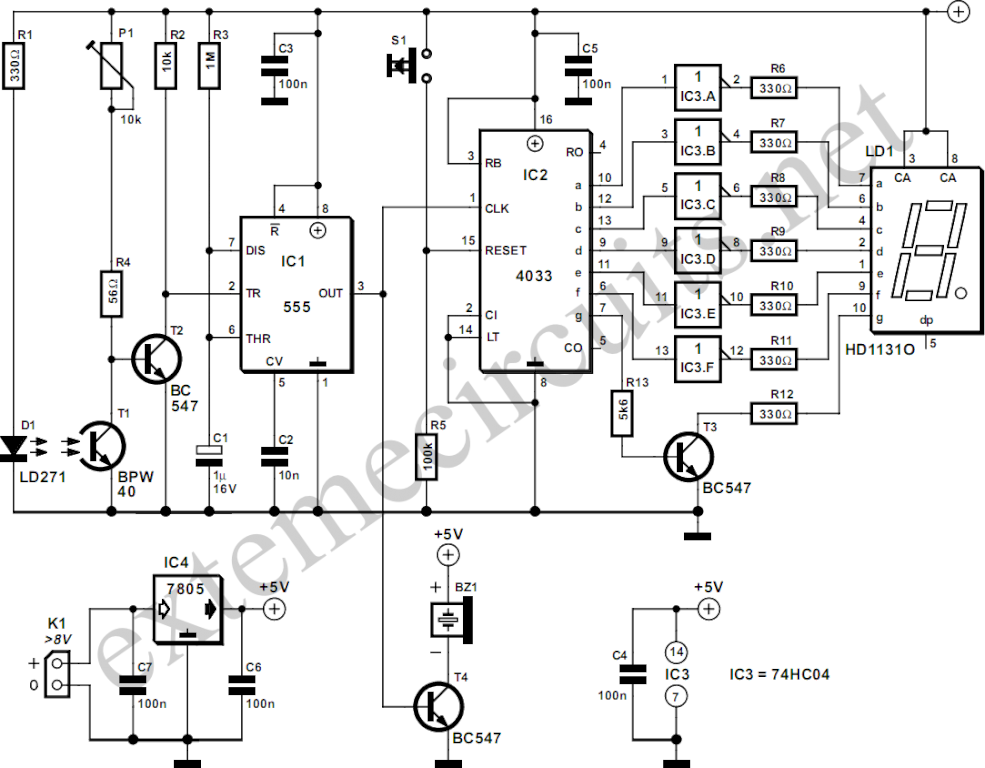

This circuit illustrates the method of cascading counters while maintaining the appropriate leading zero blanking. A NAND gate is employed to determine if a digit is active, as indicated by the activation of either segment a or b on any unblanked number. The flip-flop is triggered by the least significant digit of the high-order counter, provided that this digit is not blanked. Consequently, the Q output of the flip-flop becomes high, activating the NPN transistor, which inhibits leading zero blanking on the low-order counter.

The circuit design involves a series of counters that are connected in a cascading configuration. Each counter is responsible for counting a specific range of values, and the output from one counter serves as the input to the next. This setup allows for the counting of larger numbers than a single counter could handle alone.

The key component in this design is the NAND gate, which plays a crucial role in detecting whether any of the segments (specifically segments a or b) are active. This detection is essential for maintaining the correct display of digits, particularly when leading zeros are involved. The NAND gate's output will only be low when both inputs are high, indicating that the digit is not blanked and is actively displaying a value.

The flip-flop, which is clocked by the least significant digit of the high-order counter, serves to control the leading zero blanking mechanism. When the conditions are met (i.e., the least significant digit is not blanked), the flip-flop's Q output transitions to a high state. This transition activates the NPN transistor, which is configured to inhibit the leading zero blanking on the low-order counter. As a result, the low-order counter can display its value without being suppressed by the blanking function, allowing for a more accurate representation of the overall count.

In practical applications, such a circuit is useful in digital displays where leading zeros may need to be suppressed under certain conditions. The cascading counters, along with the NAND gate and flip-flop configuration, work in harmony to ensure that the display remains clear and informative, accurately reflecting the counted value without unnecessary leading zeros.This circuit shows how to cascade counters and retain correct leading zero blanking. The NAND gate detects whether a digit is active since one of the two segments a or b is active on any unblanked number. The flip flop is clocked by the least significant digit of the high order counter, and if this digit is not blanked.

the Q output of the flip flop goes high and turns on the npn transistor, thereby inhibiting leading zero blanking on the low order counter.

The circuit design involves a series of counters that are connected in a cascading configuration. Each counter is responsible for counting a specific range of values, and the output from one counter serves as the input to the next. This setup allows for the counting of larger numbers than a single counter could handle alone.

The key component in this design is the NAND gate, which plays a crucial role in detecting whether any of the segments (specifically segments a or b) are active. This detection is essential for maintaining the correct display of digits, particularly when leading zeros are involved. The NAND gate's output will only be low when both inputs are high, indicating that the digit is not blanked and is actively displaying a value.

The flip-flop, which is clocked by the least significant digit of the high-order counter, serves to control the leading zero blanking mechanism. When the conditions are met (i.e., the least significant digit is not blanked), the flip-flop's Q output transitions to a high state. This transition activates the NPN transistor, which is configured to inhibit the leading zero blanking on the low-order counter. As a result, the low-order counter can display its value without being suppressed by the blanking function, allowing for a more accurate representation of the overall count.

In practical applications, such a circuit is useful in digital displays where leading zeros may need to be suppressed under certain conditions. The cascading counters, along with the NAND gate and flip-flop configuration, work in harmony to ensure that the display remains clear and informative, accurately reflecting the counted value without unnecessary leading zeros.This circuit shows how to cascade counters and retain correct leading zero blanking. The NAND gate detects whether a digit is active since one of the two segments a or b is active on any unblanked number. The flip flop is clocked by the least significant digit of the high order counter, and if this digit is not blanked.

the Q output of the flip flop goes high and turns on the npn transistor, thereby inhibiting leading zero blanking on the low order counter.