Bedside lamp with CD production delay

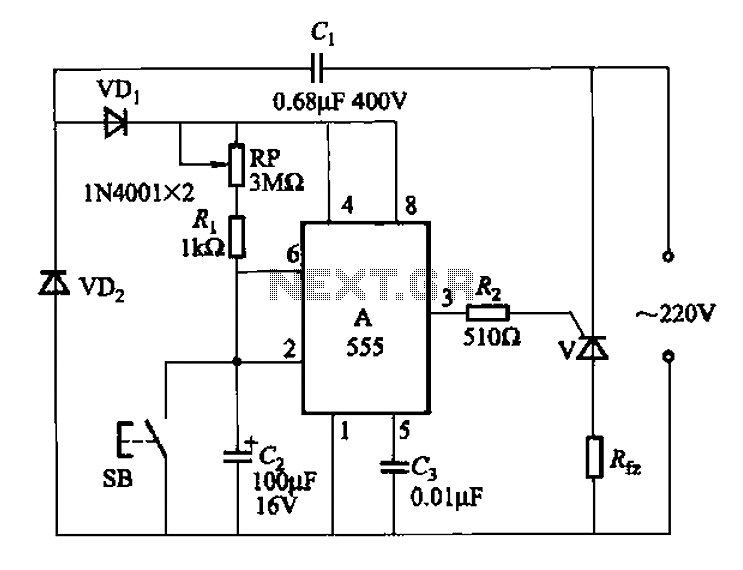

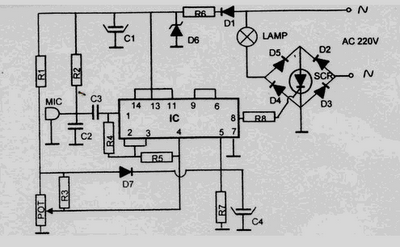

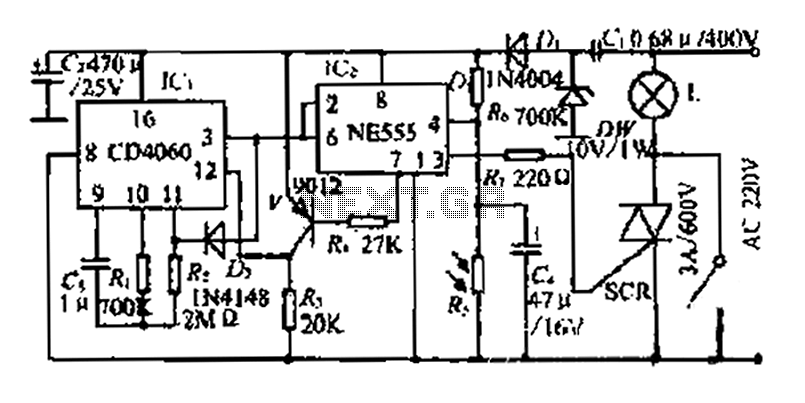

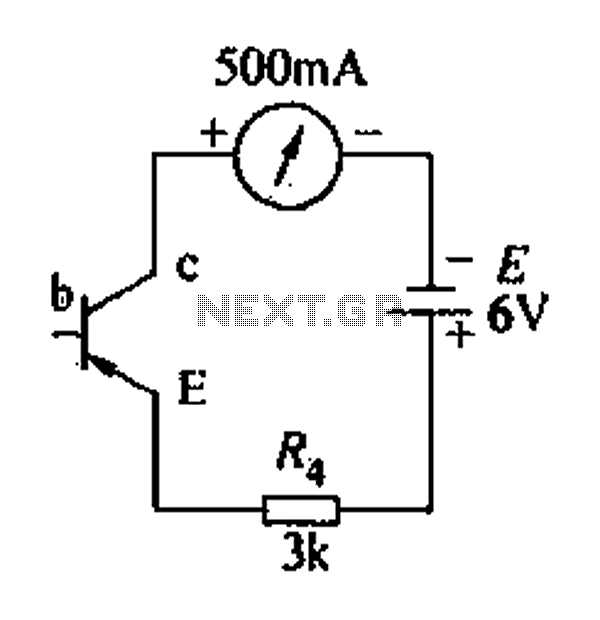

The FIG inverter I, II, along with resistors R1, R2, capacitor CI, and switch SB, forms a bistable trigger switch. Each time switch SB is activated, the output level of anti-phase II changes. The circuit includes components R3, C2, and diode VD. An inverting clamor I functions as a monostable delay circuit; adjusting the values of R3 or C2 alters the delay time of the circuit. Inverters V and f are used in parallel to enhance their driving capability. Transistors VT and surrounding resistors create a zero-trigger SCR circuit; when the SCR is activated, lamp H illuminates, and when it is deactivated, lamp H turns off. The circuit utilizes 220V AC power, which is stepped down through resistor R8 and rectified by diodes VD4, VD5, and VD6 to provide a stable regulated output voltage of 6V DC for the entire circuit.

The described circuit utilizes a bistable trigger mechanism, which allows for two stable output states. The activation of switch SB transitions the output from one state to another, effectively functioning as a toggle switch. The timing characteristics of the circuit are adjustable by modifying the resistance or capacitance values of R3 and C2, which directly influence the delay time of the monostable circuit.

The inverters V and f, connected in parallel, ensure that the circuit can drive higher loads, improving the overall performance and reliability of the output signal. The zero-trigger SCR circuit, composed of transistors VT and associated resistors, is designed to control the operation of lamp H. The SCR remains in a conductive state when triggered and will turn off when the triggering signal is removed, allowing for efficient control of the lamp based on the circuit's input conditions.

Powering the circuit with 220V AC involves a voltage reduction through resistor R8, which limits the current flowing into the rectification stage. The diodes VD4, VD5, and VD6 serve to convert the AC voltage into a stable 6V DC, ensuring that the entire circuit operates within safe voltage levels while providing sufficient power for all components. This design emphasizes reliability and efficiency, making it suitable for various applications where bistable switching and delayed timing are required.FIG inverter I, II and R1, R2, CI and SB constitute bistable trigger switch, each time the switch SB, the anti- phase II level to the output of a change. Composition R3, C2, VD 1 inverting clamor I, t monostable delay circuit, adjust the value of the entire R3 or C2 can change the delay time of the circuit. Inverters V, f used in parallel to increase their ability to drive. VT transistors and peripheral resistors vs SCR zero trigger circuit, when vs turned on the lamp lit H: vs turned off, the lamp H goes out.

220V AC power via a resistor R8 buck, diode VD4, VD5 rectifier, VD6 stable regulated output voltage DC 6V for the use of the entire circuit.

The described circuit utilizes a bistable trigger mechanism, which allows for two stable output states. The activation of switch SB transitions the output from one state to another, effectively functioning as a toggle switch. The timing characteristics of the circuit are adjustable by modifying the resistance or capacitance values of R3 and C2, which directly influence the delay time of the monostable circuit.

The inverters V and f, connected in parallel, ensure that the circuit can drive higher loads, improving the overall performance and reliability of the output signal. The zero-trigger SCR circuit, composed of transistors VT and associated resistors, is designed to control the operation of lamp H. The SCR remains in a conductive state when triggered and will turn off when the triggering signal is removed, allowing for efficient control of the lamp based on the circuit's input conditions.

Powering the circuit with 220V AC involves a voltage reduction through resistor R8, which limits the current flowing into the rectification stage. The diodes VD4, VD5, and VD6 serve to convert the AC voltage into a stable 6V DC, ensuring that the entire circuit operates within safe voltage levels while providing sufficient power for all components. This design emphasizes reliability and efficiency, making it suitable for various applications where bistable switching and delayed timing are required.FIG inverter I, II and R1, R2, CI and SB constitute bistable trigger switch, each time the switch SB, the anti- phase II level to the output of a change. Composition R3, C2, VD 1 inverting clamor I, t monostable delay circuit, adjust the value of the entire R3 or C2 can change the delay time of the circuit. Inverters V, f used in parallel to increase their ability to drive. VT transistors and peripheral resistors vs SCR zero trigger circuit, when vs turned on the lamp lit H: vs turned off, the lamp H goes out.

220V AC power via a resistor R8 buck, diode VD4, VD5 rectifier, VD6 stable regulated output voltage DC 6V for the use of the entire circuit.