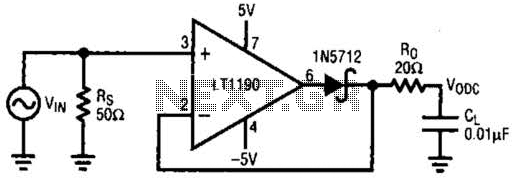

Closed-Loop Peak Detector Circuit

This closed-loop peak detector circuit utilizes a Schottky diode within the feedback loop to achieve high accuracy. The 20-ohm resistance RQ serves to isolate the 0.01-ohm load and prevent oscillations. The direct current (DC) value is measured using a digital voltmeter (DVM). At low frequencies, the error is minimal and primarily influenced by the decay of the detector capacitor between cycles. As the frequency increases, the error also escalates due to the reduced charging time of the capacitor. During this period, the overdrive becomes a negligible part of a sine-wave cycle. Notably, at around 4 MHz, the error increases significantly due to the slew-rate limitations of the operational amplifier.

The closed-loop peak detector circuit is designed to capture and hold the peak value of an input signal, ensuring that the output accurately reflects the maximum amplitude of the waveform. The inclusion of a Schottky diode in the feedback loop is critical for maintaining precision, as this type of diode has a low forward voltage drop and fast switching capabilities. This enhances the responsiveness of the circuit to rapid changes in the input signal.

The 20-ohm resistor, labeled RQ, plays a crucial role in isolating the load from the detection circuit, which is vital for stability. By preventing oscillations, RQ ensures that the output remains steady and accurate, particularly in dynamic environments where the input signal may vary significantly.

The use of a digital voltmeter (DVM) for reading the DC value allows for precise measurements, making it suitable for applications where accuracy is paramount. The performance of the peak detector is frequency-dependent; at lower frequencies, the decay of the capacitor charge between cycles is manageable, leading to minimal error. However, as the frequency increases, the time available for the capacitor to charge diminishes, resulting in increased error margins. This effect is particularly pronounced at high frequencies, where the operational amplifier's slew rate becomes a limiting factor. The slew rate defines how quickly the output of the op-amp can change in response to a rapid input signal, and when the frequency approaches 4 MHz, the limitations become significant enough to cause a noticeable rise in error.

Overall, this closed-loop peak detector circuit is an effective solution for accurately capturing peak values in high-frequency applications, provided that careful consideration is given to component selection and circuit design to mitigate the effects of frequency-related errors. This closed-loop peak detector circuit uses a Schottky diode inside feedback loop to obtain good accuracy. The 20- resistance RQ isolates the 0.01- load and prevents oscillation. The dc value is read with a DVM. At a low frequency, the error is small and dominated by the decay of the detector capacitor between cycles.

As the frequency rises, the error increases because capacitor charging time decreases. During this time, the overdrive becomes a very small portion of a sine-wave cycle. Finally, at approximately 4 MHz, the error rises rapidly because of the slew- rate limitation of the op amp.

The closed-loop peak detector circuit is designed to capture and hold the peak value of an input signal, ensuring that the output accurately reflects the maximum amplitude of the waveform. The inclusion of a Schottky diode in the feedback loop is critical for maintaining precision, as this type of diode has a low forward voltage drop and fast switching capabilities. This enhances the responsiveness of the circuit to rapid changes in the input signal.

The 20-ohm resistor, labeled RQ, plays a crucial role in isolating the load from the detection circuit, which is vital for stability. By preventing oscillations, RQ ensures that the output remains steady and accurate, particularly in dynamic environments where the input signal may vary significantly.

The use of a digital voltmeter (DVM) for reading the DC value allows for precise measurements, making it suitable for applications where accuracy is paramount. The performance of the peak detector is frequency-dependent; at lower frequencies, the decay of the capacitor charge between cycles is manageable, leading to minimal error. However, as the frequency increases, the time available for the capacitor to charge diminishes, resulting in increased error margins. This effect is particularly pronounced at high frequencies, where the operational amplifier's slew rate becomes a limiting factor. The slew rate defines how quickly the output of the op-amp can change in response to a rapid input signal, and when the frequency approaches 4 MHz, the limitations become significant enough to cause a noticeable rise in error.

Overall, this closed-loop peak detector circuit is an effective solution for accurately capturing peak values in high-frequency applications, provided that careful consideration is given to component selection and circuit design to mitigate the effects of frequency-related errors. This closed-loop peak detector circuit uses a Schottky diode inside feedback loop to obtain good accuracy. The 20- resistance RQ isolates the 0.01- load and prevents oscillation. The dc value is read with a DVM. At a low frequency, the error is small and dominated by the decay of the detector capacitor between cycles.

As the frequency rises, the error increases because capacitor charging time decreases. During this time, the overdrive becomes a very small portion of a sine-wave cycle. Finally, at approximately 4 MHz, the error rises rapidly because of the slew- rate limitation of the op amp.