CMOS and ECL mutual interface circuit b

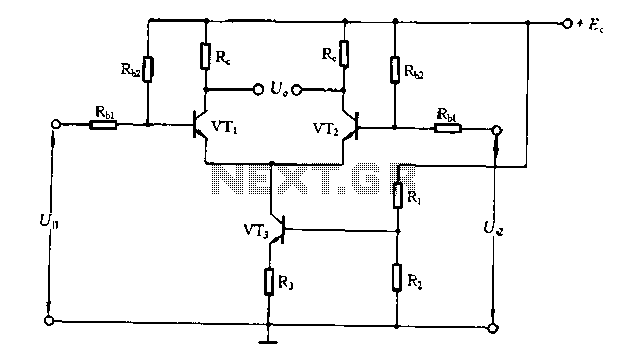

ECL integrated circuit non-saturated digital logic circuits. CMOS and ECL interface circuit shown in cross.

ECL (Emitter Coupled Logic) integrated circuits are designed to operate in a non-saturated mode, providing high-speed digital logic functionality. These circuits are characterized by their fast switching speeds and low propagation delays, making them suitable for high-performance applications. The integration of ECL with CMOS (Complementary Metal-Oxide-Semiconductor) technology allows for efficient interfacing between different logic families, leveraging the strengths of both technologies.

In a typical ECL circuit, the logic levels are determined by the voltage differences between the emitter terminals of bipolar junction transistors (BJTs). The non-saturation operation ensures that the transistors remain in their active region, allowing for rapid transitions and minimizing the time spent in the saturation state, which can slow down switching speeds. This characteristic is particularly beneficial in applications that require high-frequency operation and low power consumption.

The interface circuit between CMOS and ECL is crucial for ensuring compatibility between the two logic families. This interface typically includes level shifters and buffers that translate the voltage levels and signal characteristics of CMOS to those of ECL. The design must consider the voltage thresholds of both technologies to maintain signal integrity and prevent logic errors.

In summary, ECL integrated circuits provide non-saturated digital logic capabilities with high-speed performance, and their integration with CMOS technology facilitates effective communication between different logic families, enhancing overall system efficiency.ECL integrated circuit non-saturated digital logic circuits. CMOS and ECL interface circuit shown in cross

ECL (Emitter Coupled Logic) integrated circuits are designed to operate in a non-saturated mode, providing high-speed digital logic functionality. These circuits are characterized by their fast switching speeds and low propagation delays, making them suitable for high-performance applications. The integration of ECL with CMOS (Complementary Metal-Oxide-Semiconductor) technology allows for efficient interfacing between different logic families, leveraging the strengths of both technologies.

In a typical ECL circuit, the logic levels are determined by the voltage differences between the emitter terminals of bipolar junction transistors (BJTs). The non-saturation operation ensures that the transistors remain in their active region, allowing for rapid transitions and minimizing the time spent in the saturation state, which can slow down switching speeds. This characteristic is particularly beneficial in applications that require high-frequency operation and low power consumption.

The interface circuit between CMOS and ECL is crucial for ensuring compatibility between the two logic families. This interface typically includes level shifters and buffers that translate the voltage levels and signal characteristics of CMOS to those of ECL. The design must consider the voltage thresholds of both technologies to maintain signal integrity and prevent logic errors.

In summary, ECL integrated circuits provide non-saturated digital logic capabilities with high-speed performance, and their integration with CMOS technology facilitates effective communication between different logic families, enhancing overall system efficiency.ECL integrated circuit non-saturated digital logic circuits. CMOS and ECL interface circuit shown in cross