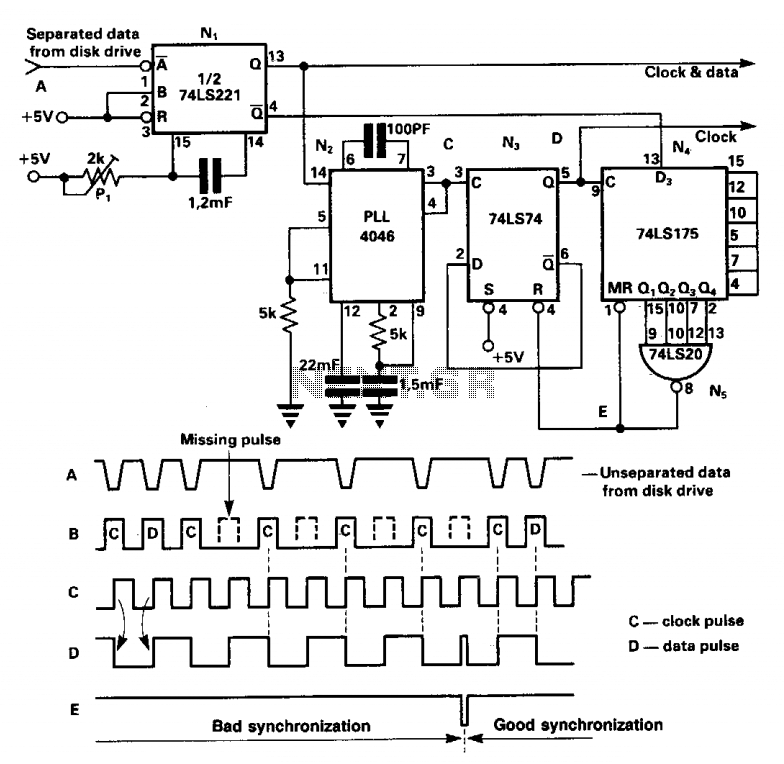

Data separator

The data separator is designed for use with 8-inch flexible diskettes utilizing the IBM 3870 soft sectored format. The circuit provides data and clock signal (B) along with clock pulses (D). These signals must be sequenced such that the negative edge of the clock pulse aligns with the midpoint of a data cell. Unseparated data (A) from the floppy drive is processed through a one-shot circuit (Nl). Trimmer (PI) should be calibrated to ensure that pulses (B) are 1 µs wide. This signal is used to synchronize Phase-Locked Loop (PLL) (N2) with a free-running frequency set to 500 kHz. Additionally, the output of the PLL is 90 degrees out of phase with its input. The D-type flip-flop (N3) is configured as a frequency divider, changing state at each positive edge of signal (C). Flip-flop (N4), set up as a shift register, monitors for four consecutive missing pulses. Upon detection of this condition, the circuit is resynchronized using signal (E) to ensure that the negative edge of signal (D) is positioned in the center of a data cell.

The data separator circuit is crucial for accurately processing information from 8-inch floppy diskettes formatted in the IBM 3870 standard. Its primary function is to separate and synchronize data and clock signals, ensuring that data is read correctly from the diskette. The circuit employs a one-shot multivibrator (Nl) to shape the unseparated data signal (A), providing a clean output that is essential for reliable data transmission.

The adjustment of trimmer (PI) to achieve a pulse width of 1 µs for signal (B) is a critical step. This calibration ensures that the PLL (N2) can maintain synchronization with the incoming data stream, operating at a stable frequency of 500 kHz. The PLL's output being 90 degrees out of phase is an intentional design choice that allows for effective phase comparison and adjustment, further enhancing the reliability of the data separation process.

The D-type flip-flop (N3) serves as a frequency divider, effectively halving the frequency of the input signal (C) and generating a corresponding output that is used in the subsequent stages of the circuit. Meanwhile, flip-flop (N4) operates as a shift register, continuously monitoring the incoming pulse stream for any interruptions. The detection of four consecutive missing pulses indicates a potential loss of synchronization, prompting the circuit to reestablish alignment using signal (E). This self-correcting mechanism is vital for maintaining data integrity, ensuring that the negative edge of clock pulse (D) remains accurately positioned within the data cell, thus facilitating proper data recovery from the floppy diskette.

Overall, the design of the data separator circuit illustrates a sophisticated approach to handling legacy data storage formats, emphasizing the importance of timing and synchronization in digital signal processing.The data separator is intended for use with 8" flexible diskettes with IBM 3870 soft sectored format. The circuit delivers data and clock (B) and clock pulses (D). These two signals must be in such a sequence that the negative edge of the clock pulse is at the middle of a data cell.

Unseparated data (A) from the floppy unit is shaped with one shot Nl. Trimmer PI should be adjusted so that pulses (B) are 1 ?& wide. This signal synchronizes PLL N2 with a free running frequency adjusted to 500 kHz. The output of the PLL is 90° out of phase with its input. D-type flip-flop N3 is connected as a divider by two and changes state at each positive edge of (C). N4, connected as a shift register, looks for four consecutive missing pulses. When this happens, the circuit is resynchronized with (E) so that the negative edge of (D) is in the middle of a data cell.

The data separator circuit is crucial for accurately processing information from 8-inch floppy diskettes formatted in the IBM 3870 standard. Its primary function is to separate and synchronize data and clock signals, ensuring that data is read correctly from the diskette. The circuit employs a one-shot multivibrator (Nl) to shape the unseparated data signal (A), providing a clean output that is essential for reliable data transmission.

The adjustment of trimmer (PI) to achieve a pulse width of 1 µs for signal (B) is a critical step. This calibration ensures that the PLL (N2) can maintain synchronization with the incoming data stream, operating at a stable frequency of 500 kHz. The PLL's output being 90 degrees out of phase is an intentional design choice that allows for effective phase comparison and adjustment, further enhancing the reliability of the data separation process.

The D-type flip-flop (N3) serves as a frequency divider, effectively halving the frequency of the input signal (C) and generating a corresponding output that is used in the subsequent stages of the circuit. Meanwhile, flip-flop (N4) operates as a shift register, continuously monitoring the incoming pulse stream for any interruptions. The detection of four consecutive missing pulses indicates a potential loss of synchronization, prompting the circuit to reestablish alignment using signal (E). This self-correcting mechanism is vital for maintaining data integrity, ensuring that the negative edge of clock pulse (D) remains accurately positioned within the data cell, thus facilitating proper data recovery from the floppy diskette.

Overall, the design of the data separator circuit illustrates a sophisticated approach to handling legacy data storage formats, emphasizing the importance of timing and synchronization in digital signal processing.The data separator is intended for use with 8" flexible diskettes with IBM 3870 soft sectored format. The circuit delivers data and clock (B) and clock pulses (D). These two signals must be in such a sequence that the negative edge of the clock pulse is at the middle of a data cell.

Unseparated data (A) from the floppy unit is shaped with one shot Nl. Trimmer PI should be adjusted so that pulses (B) are 1 ?& wide. This signal synchronizes PLL N2 with a free running frequency adjusted to 500 kHz. The output of the PLL is 90° out of phase with its input. D-type flip-flop N3 is connected as a divider by two and changes state at each positive edge of (C). N4, connected as a shift register, looks for four consecutive missing pulses. When this happens, the circuit is resynchronized with (E) so that the negative edge of (D) is in the middle of a data cell.