Homebuilt video digitiser MkII circuit description

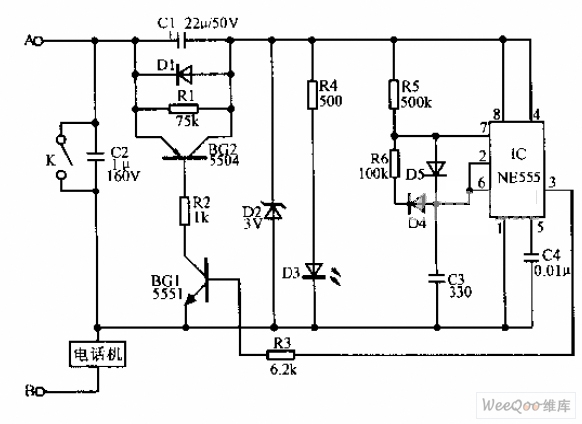

A video digitizer, also known as a frame grabber, captures still picture frames from a television set, video camera, or video recorder, and transmits them to a computer for display, storage, or manipulation. This document outlines the Mark II version of a home-built digitizer that interfaces with an EPP parallel port on IBM PCs. The Mark II supports color captures with PAL/NTSC decoding performed in software. It is important to note that the Bt218 chip, which is the foundation of this project, was discontinued in 2000. For those intending to build this project as specified, it is essential to source old stock of the chip. Alternatively, the circuit could be adapted to utilize a different low-cost ADC, such as the TDA8703 from Philips, although details for this adaptation are not provided. Any PC hardware capable of running the mentioned operating systems should be sufficient for the software, although a faster PC will generally yield better performance, especially for colorization, which may be slow on systems below Pentium specifications. An EPP-type parallel port is required; however, with software modifications, a simple bi-directional port could be employed, albeit with reduced speed. The digitizer captures only one of the two interlace fields, with the second field often resulting in motion blur. It is limited by a mere 256kB buffer. The published design captures odd/even fields randomly, but modifications can ensure that one specific field is captured consistently. The digitization clock arrangement is not fully phase-locked to the line sync, though a proper line-locked sampling clock can be implemented as an extension to the project. Typically, horizontal resolution is decreased in domestic video recording formats, and color quality is significantly degraded. For optimal results, it is recommended to use off-air signals from a good aerial. The provided image is from only one field, necessitating a doubling of the height to achieve the correct aspect ratio. Digitization occurs with a 14.161 Msps clock, which is partially phase-locked to the line sync. The ADC converts the incoming composite video signal into a digital representation, typically sampled at 15 MHz. This data rate exceeds the capacity of the parallel port, necessitating a configuration where data from the ADC is fed into a high-speed 256kB field memory. The video timing logic utilizes line and field synchronization signals from the sync-separator to ensure that storage begins and ends at field boundaries, collecting a fixed number of pixel samples for each video scan line. The PC parallel port interface logic manages the output of data from the field memory to the host PC and temporarily halts the image refresh in memory while data is being read. The MSM518221A-3Z is packaged in a "ZIG-ZAG" configuration, with two rows of pins spaced 0.1 inches apart and offset by 0.05 inches. This configuration may pose challenges for breadboard or Veroboard construction, necessitating an adapter. The circuit is organized into three sheets: one illustrating the analog and digital video signal path, including the parallel port interface; a second depicting the clock and video timing; and a third detailing the voltage regulator. The MSM518221 - WE signal enables data writing and advances the Write pointer. When low, it allows the Write pointer to advance but prevents overwriting of data. The Reset Write Pointer (RSTW) is semi-synchronous, intended to lower for only one cycle at a time, and does not hold the Write Pointer at the start indefinitely. Caution is advised when modifying the design. For the Bt218KP, the color subcarrier trap is specified with component values for the UK standard PAL; for NTSC, two 220pF capacitors in parallel should be used to create a 440pF component to attenuate the 3.5 MHz signal. The subcarrier trap is necessary only when capturing black-and-white images from color signals or when the sampling rate is insufficient to adequately sample the Fsc.

The circuit design involves several key components that facilitate the digitization process. The core of the system relies on the ADC, which performs analog-to-digital conversion of the composite video signal. The high-speed 256kB field memory serves as a temporary storage solution, buffering the digitized data before it is transmitted to the PC. The video timing logic is crucial for synchronizing the data capture process, ensuring that the samples align with the video signal's timing characteristics.

In addition to the main components, the circuit also incorporates various passive components that help filter and stabilize the signals, ensuring high-quality digitization. The power supply circuitry is designed to provide stable voltage levels to the entire system, which is critical for reliable operation. The PCB layout should take into account the signal integrity by minimizing trace lengths and using appropriate grounding techniques to reduce noise and interference.

For users interested in adapting the design for different ADCs, it is recommended to carefully analyze the timing requirements and electrical characteristics of the chosen component to ensure compatibility with the existing architecture. This may involve adjusting the clocking scheme or modifying the interface logic to accommodate different data rates. Overall, this project presents a versatile solution for capturing and digitizing video signals, with potential for further enhancements and adaptations based on user needs.A "video-digitiser" (also known as a "frame grabber") captures still pictures frames from a TV set, video camera, or video recorder, etc. , and forwards them to a computer for display, storage, or general manipulation. This document describes the MarkII version of a home-built digitiser which interfaces to an EPP parallel port on IBM PCs.

MkII supports colo ur captures (PAL/NTSC decoding in software). Note: the Bt218 chip, around which this project is based, ceased to be manufactured during the year 2000. If you want to build this project as shown, ensure you can get some old stock! Alternatively, you could adapt the circuit to work with a different low-cost ADC, such as the TDA8703 from Philips.

I have not done this myself yet, so cannot offer details. Any PC hardware capable of running the operating systems mentioned should run the software adequately, though as always, a faster PC will often result in better performance. In particular, colourisation will be very slow on anything sub-Pentium! An EPP-type parallel port is required (though with software modifications, a simple bi-directional port would be useable, with poorer speed) Still only captures one of the two interlace fields (though often the second one would lead to motion blur anyway.

). Limited by mere 256kB of buffer. Published design captures odd/even field at random, though by simple modification you could ensure one or the other is guaranteed. Digitisation clock arrangement shown is not fully phase-locked to the linesync. A proper line-locked sampling clock could quite easily be implemented as an extension to the project.

In general, horizontal resolution is decreased in domestic video recording formats (and colour is really seriously degraded). Use off-air signals from a good aerial for best results! (This image is from only one field, so the height needs to be doubled to obtain the correct aspect ratio).

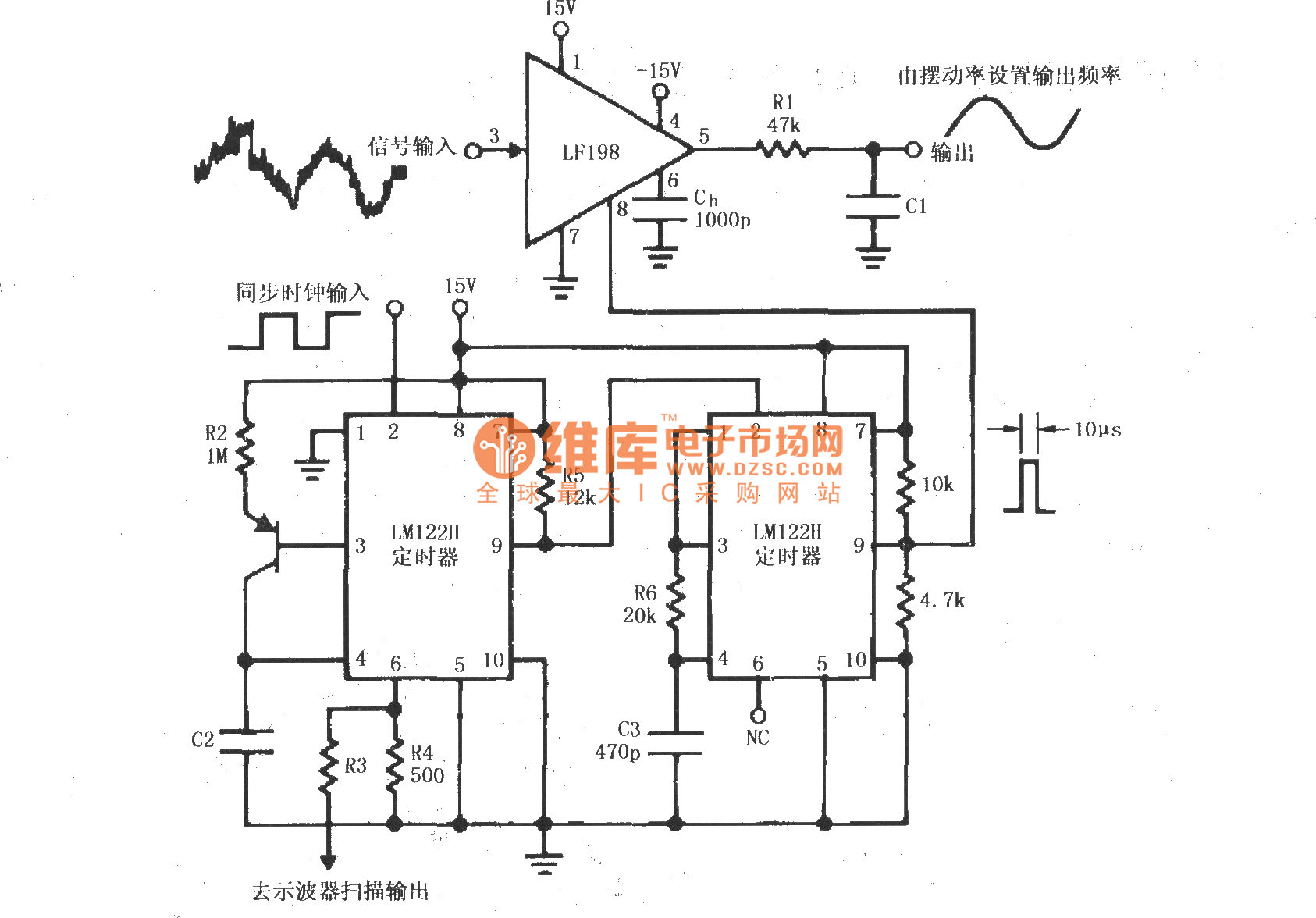

It was digitised with a 14. 161Msps clock, partially phase-locked to the line-sync. The ADC converts the incoming composite video signal to a digital representation, sampled typically at 15MHz. This data rate is far too fast for the parallel port to cope with directly, so instead the circuitry is arranged so that data from ADC is fed into a high-speed 256kB field memory.

Video timing logic uses line and field synchronisation signals from the sync-separator to ensure that storage begins and ends at field boundaries, and that a fixed number of samples (pixels) are collected for each video scan line. PC parallel port interface logic controls the output of data from the field memory to the host PC, and temporarily halts the refreshing of the image in the memory while data is being read out.

The MSM518221A-3Z is supplied in a "ZIG-ZAG" package, with two rows 0. 1" apart, of pins on 0. 1" spacing, with the two rows offset by 0. 05". This will not be an issue if designing a PCB, but for breadboard or Veroboard construction you will need to make an adapter! For convenience, the circuit is drawn in three sheets: 1) showing the analog and digital video signal path, including parallel port interface, 2) showing the clock and video timing, 3) the voltage regulator.

MSM518221 - WE enables data to be written and forward the Write pointer, IE when low, allows the write pointer to be forwarded, but inhibits overwriting of data. Reset Write Pointer (RSTW) is semi-synchronous - supposed to only lower for one cycle at a time - does NOT hold the Write Pointer at the start indefinitely!

This explains why some of the WE logic is less simple than it might be. CAUTION if modifying my design! On the Bt218KP the colour subcarrier trap is shown with component values for UK standard PAL: for NTSC, use two 220pF capacitors in paralllel to make 440pF to attenuate the 3. 5MHz signal. The subcarrier trap is ONLY required when obtaining black-and-white captures from colour signals, or when the sampling rate is too low to sample Fsc proper

🔗 External reference

The circuit design involves several key components that facilitate the digitization process. The core of the system relies on the ADC, which performs analog-to-digital conversion of the composite video signal. The high-speed 256kB field memory serves as a temporary storage solution, buffering the digitized data before it is transmitted to the PC. The video timing logic is crucial for synchronizing the data capture process, ensuring that the samples align with the video signal's timing characteristics.

In addition to the main components, the circuit also incorporates various passive components that help filter and stabilize the signals, ensuring high-quality digitization. The power supply circuitry is designed to provide stable voltage levels to the entire system, which is critical for reliable operation. The PCB layout should take into account the signal integrity by minimizing trace lengths and using appropriate grounding techniques to reduce noise and interference.

For users interested in adapting the design for different ADCs, it is recommended to carefully analyze the timing requirements and electrical characteristics of the chosen component to ensure compatibility with the existing architecture. This may involve adjusting the clocking scheme or modifying the interface logic to accommodate different data rates. Overall, this project presents a versatile solution for capturing and digitizing video signals, with potential for further enhancements and adaptations based on user needs.A "video-digitiser" (also known as a "frame grabber") captures still pictures frames from a TV set, video camera, or video recorder, etc. , and forwards them to a computer for display, storage, or general manipulation. This document describes the MarkII version of a home-built digitiser which interfaces to an EPP parallel port on IBM PCs.

MkII supports colo ur captures (PAL/NTSC decoding in software). Note: the Bt218 chip, around which this project is based, ceased to be manufactured during the year 2000. If you want to build this project as shown, ensure you can get some old stock! Alternatively, you could adapt the circuit to work with a different low-cost ADC, such as the TDA8703 from Philips.

I have not done this myself yet, so cannot offer details. Any PC hardware capable of running the operating systems mentioned should run the software adequately, though as always, a faster PC will often result in better performance. In particular, colourisation will be very slow on anything sub-Pentium! An EPP-type parallel port is required (though with software modifications, a simple bi-directional port would be useable, with poorer speed) Still only captures one of the two interlace fields (though often the second one would lead to motion blur anyway.

). Limited by mere 256kB of buffer. Published design captures odd/even field at random, though by simple modification you could ensure one or the other is guaranteed. Digitisation clock arrangement shown is not fully phase-locked to the linesync. A proper line-locked sampling clock could quite easily be implemented as an extension to the project.

In general, horizontal resolution is decreased in domestic video recording formats (and colour is really seriously degraded). Use off-air signals from a good aerial for best results! (This image is from only one field, so the height needs to be doubled to obtain the correct aspect ratio).

It was digitised with a 14. 161Msps clock, partially phase-locked to the line-sync. The ADC converts the incoming composite video signal to a digital representation, sampled typically at 15MHz. This data rate is far too fast for the parallel port to cope with directly, so instead the circuitry is arranged so that data from ADC is fed into a high-speed 256kB field memory.

Video timing logic uses line and field synchronisation signals from the sync-separator to ensure that storage begins and ends at field boundaries, and that a fixed number of samples (pixels) are collected for each video scan line. PC parallel port interface logic controls the output of data from the field memory to the host PC, and temporarily halts the refreshing of the image in the memory while data is being read out.

The MSM518221A-3Z is supplied in a "ZIG-ZAG" package, with two rows 0. 1" apart, of pins on 0. 1" spacing, with the two rows offset by 0. 05". This will not be an issue if designing a PCB, but for breadboard or Veroboard construction you will need to make an adapter! For convenience, the circuit is drawn in three sheets: 1) showing the analog and digital video signal path, including parallel port interface, 2) showing the clock and video timing, 3) the voltage regulator.

MSM518221 - WE enables data to be written and forward the Write pointer, IE when low, allows the write pointer to be forwarded, but inhibits overwriting of data. Reset Write Pointer (RSTW) is semi-synchronous - supposed to only lower for one cycle at a time - does NOT hold the Write Pointer at the start indefinitely!

This explains why some of the WE logic is less simple than it might be. CAUTION if modifying my design! On the Bt218KP the colour subcarrier trap is shown with component values for UK standard PAL: for NTSC, use two 220pF capacitors in paralllel to make 440pF to attenuate the 3. 5MHz signal. The subcarrier trap is ONLY required when obtaining black-and-white captures from colour signals, or when the sampling rate is too low to sample Fsc proper

🔗 External reference