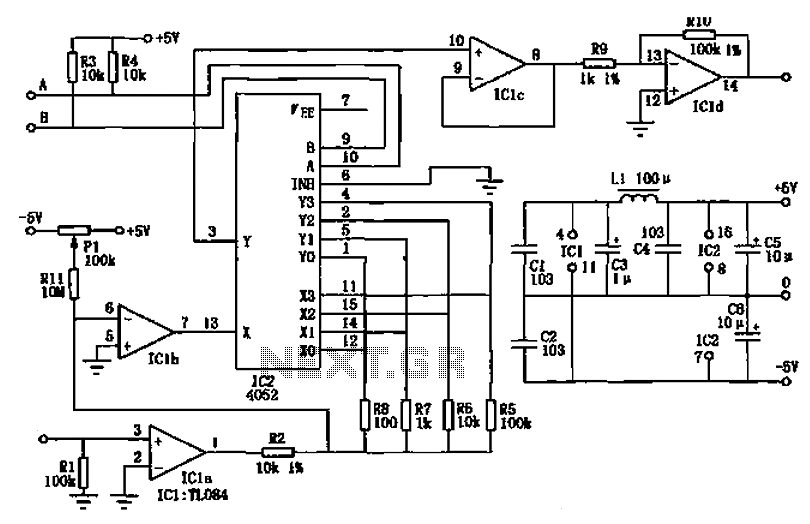

Improved one-shot timer circuit composed of 2 PUT

Figure 1 illustrates an enhanced trigger timing circuit that utilizes two Programmable Unijunction Transistors (PUTs). When a set signal is applied, the circuit is activated, causing transistor VT1 to enter the conduction state and energizing relay K. This action simultaneously supplies voltage for the delay circuit, allowing capacitor C1 to charge. As a result, PUT1 is activated by the positive voltage, and capacitor C1 influences the operation of PUT1.

The improved trigger timing circuit is designed to provide precise control over timing applications. The circuit's functionality begins when a set signal is applied to the input, which initiates the conduction of VT1. This conduction allows current to flow through the relay K, effectively energizing it and enabling its contacts to close, thus providing power to the subsequent components in the circuit.

Simultaneously, the charging process of capacitor C1 begins. The charging rate of C1 is determined by the resistor-capacitor (RC) time constant, which dictates how quickly the capacitor reaches a certain voltage level. As C1 charges, it provides a stable voltage to PUT1, allowing it to turn on once the voltage across it exceeds its threshold. The interaction between C1 and PUT1 is critical, as it sets the timing for the entire circuit operation.

The use of two PUTs enhances the circuit's performance by allowing for more precise control over the timing intervals. The first PUT can be configured to respond to the voltage across C1, while the second PUT can be used to manage the discharge cycle, ensuring that the timing sequence is both reliable and adjustable. The overall design of the circuit provides flexibility in applications such as delay timers, pulse generators, and other timing-related functions in electronic systems.

In summary, this improved trigger timing circuit effectively integrates the characteristics of PUTs and capacitors to create a robust timing solution, capable of delivering accurate and repeatable results in various electronic applications.Figure 1 is an improved trigger timing circuit composed of 2 PUT. If you add the set signal, the circuit will be set, transistor VT1 turn to the conduction state, the relay K will be energized action. It supplies voltage for the delay voltage at the same time. Therefore, the capacitor is charged by C1. PUT1 is conducted by positive voltage. C1 passes PUT1,.. 🔗 External reference

The improved trigger timing circuit is designed to provide precise control over timing applications. The circuit's functionality begins when a set signal is applied to the input, which initiates the conduction of VT1. This conduction allows current to flow through the relay K, effectively energizing it and enabling its contacts to close, thus providing power to the subsequent components in the circuit.

Simultaneously, the charging process of capacitor C1 begins. The charging rate of C1 is determined by the resistor-capacitor (RC) time constant, which dictates how quickly the capacitor reaches a certain voltage level. As C1 charges, it provides a stable voltage to PUT1, allowing it to turn on once the voltage across it exceeds its threshold. The interaction between C1 and PUT1 is critical, as it sets the timing for the entire circuit operation.

The use of two PUTs enhances the circuit's performance by allowing for more precise control over the timing intervals. The first PUT can be configured to respond to the voltage across C1, while the second PUT can be used to manage the discharge cycle, ensuring that the timing sequence is both reliable and adjustable. The overall design of the circuit provides flexibility in applications such as delay timers, pulse generators, and other timing-related functions in electronic systems.

In summary, this improved trigger timing circuit effectively integrates the characteristics of PUTs and capacitors to create a robust timing solution, capable of delivering accurate and repeatable results in various electronic applications.Figure 1 is an improved trigger timing circuit composed of 2 PUT. If you add the set signal, the circuit will be set, transistor VT1 turn to the conduction state, the relay K will be energized action. It supplies voltage for the delay voltage at the same time. Therefore, the capacitor is charged by C1. PUT1 is conducted by positive voltage. C1 passes PUT1,.. 🔗 External reference