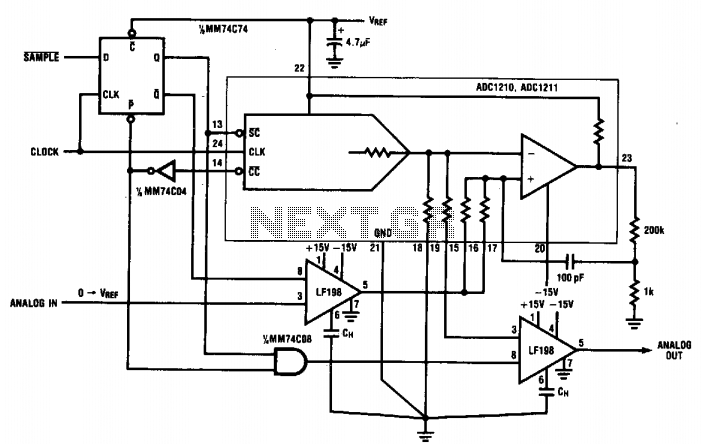

Infinite sample and hold amplifier

During normal hold mode, the replicated analog voltage is buffered directly through the sample-and-hold (S/H) amplifier to the output. Upon receiving a SAMPLE signal, the S/H amplifier enters hold mode, maintaining the voltage until the new analog voltage is valid. The same SAMPLE signal also initiates an update to the input sample-and-hold amplifier, capturing and holding the most recent analog voltage for conversion. The previously determined voltage remains stable at the output throughout the conversion cycle, while the successive approximation register (SAR) digital-to-analog (D/A) converter continuously adjusts to replicate the new input voltage. At the conclusion of the conversion, the output sample-and-hold amplifier is returned to track mode, allowing the new analog voltage to be regenerated.

The described circuit operates on the principles of sample-and-hold technology, which is crucial in analog-to-digital conversion processes. The S/H amplifier serves as a critical component in maintaining signal integrity during the conversion cycle. In normal operation, the S/H amplifier buffers the analog voltage, ensuring that the output reflects the input accurately. When the SAMPLE signal is activated, the S/H amplifier transitions to hold mode, effectively freezing the output voltage. This is essential for preventing any fluctuations in the output during the conversion process, which could lead to inaccuracies.

The input sample-and-hold amplifier is responsible for capturing the latest analog voltage. This action is synchronized with the SAMPLE signal, ensuring that the most current voltage is held stable for conversion. The SAR D/A converter plays a pivotal role in adjusting the output to match the new input voltage, continuously refining its output to minimize discrepancies between the actual and desired voltages.

Once the conversion is complete, the output S/H amplifier reverts to track mode, allowing it to follow the new analog voltage. This transition is critical as it enables the system to adapt to changes in the input signal, maintaining accuracy and responsiveness in real-time applications. Overall, the circuit's design emphasizes precision and reliability, making it suitable for various applications in signal processing and digital communication systems.During normal' 'hold'' mode, the replicated analog voltage is buffered straight through the S/H amplifier to the output. Upon issuance of a SAMPLE signal, the S/H amplifier is placed in the hold mode, holding the voltage until the new analog voltage is valid.

The same SAMPLE signal triggers an update to the input sample-and-hold amplifier. The most current analog voltage is captured and held for conversion. The previously determined voltage is held stable at the output during the conversion cycle while the SAR/D-to-A converter continuously adjusts to replicate the new input voltage. At the end of the conversion, the output sample-and-hold amplifier is once again placed in the track mode. The new analog voltage is then regenerated.

The described circuit operates on the principles of sample-and-hold technology, which is crucial in analog-to-digital conversion processes. The S/H amplifier serves as a critical component in maintaining signal integrity during the conversion cycle. In normal operation, the S/H amplifier buffers the analog voltage, ensuring that the output reflects the input accurately. When the SAMPLE signal is activated, the S/H amplifier transitions to hold mode, effectively freezing the output voltage. This is essential for preventing any fluctuations in the output during the conversion process, which could lead to inaccuracies.

The input sample-and-hold amplifier is responsible for capturing the latest analog voltage. This action is synchronized with the SAMPLE signal, ensuring that the most current voltage is held stable for conversion. The SAR D/A converter plays a pivotal role in adjusting the output to match the new input voltage, continuously refining its output to minimize discrepancies between the actual and desired voltages.

Once the conversion is complete, the output S/H amplifier reverts to track mode, allowing it to follow the new analog voltage. This transition is critical as it enables the system to adapt to changes in the input signal, maintaining accuracy and responsiveness in real-time applications. Overall, the circuit's design emphasizes precision and reliability, making it suitable for various applications in signal processing and digital communication systems.During normal' 'hold'' mode, the replicated analog voltage is buffered straight through the S/H amplifier to the output. Upon issuance of a SAMPLE signal, the S/H amplifier is placed in the hold mode, holding the voltage until the new analog voltage is valid.

The same SAMPLE signal triggers an update to the input sample-and-hold amplifier. The most current analog voltage is captured and held for conversion. The previously determined voltage is held stable at the output during the conversion cycle while the SAR/D-to-A converter continuously adjusts to replicate the new input voltage. At the end of the conversion, the output sample-and-hold amplifier is once again placed in the track mode. The new analog voltage is then regenerated.