Internal functional block diagram of NCP5201

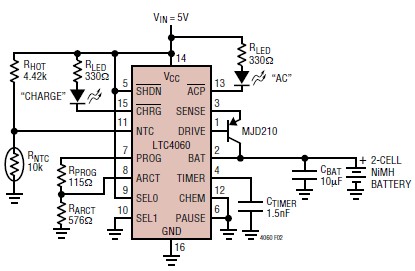

The NCP5201 chip contains two sets of PWM signal generating circuits, each with a dedicated set of output pins. These circuits produce two opposite phase PWM signals, which are applied to the gates of three field effect transistors. This arrangement allows the field effect transistors to alternately turn on, converting the battery supply voltage into a pulse voltage. The pulse voltage is then filtered by inductor L2 and capacitor COUT to provide a +2.5 V voltage supply for memory. Additionally, this +2.5 V power supply is used within the chip to power a second PWM signal generating circuit and two more field-effect transistors. These transistors convert the 2.5 V into a pulse signal, which is output from the chip. Capacitors C14, C15, and C16 filter this output to produce a DC voltage of 1.25 V, supplying power to the memory circuit.

The NCP5201 is designed to efficiently manage power conversion through the use of pulse width modulation (PWM) techniques. The chip operates by generating two sets of PWM signals that are out of phase, allowing for efficient control of the field effect transistors (FETs). The alternating operation of the FETs ensures that the battery supply voltage is effectively transformed into a pulsed output, which is crucial for applications that require a stable voltage supply.

In the first stage, the PWM signals control the gates of the FETs, enabling them to switch on and off rapidly. This switching action is what allows the circuit to convert the DC battery voltage into a pulsed output. The inductor L2 and capacitor COUT play a vital role in smoothing out the pulsed voltage, resulting in a stable +2.5 V output. This voltage is essential for the operation of memory circuits, which often require a specific voltage level for optimal performance.

Furthermore, the internal circuitry of the NCP5201 utilizes the +2.5 V supply to power a second PWM generation circuit. This circuit operates similarly to the first, utilizing two additional FETs to produce another pulsed output signal. The output from this second stage is filtered through capacitors C14, C15, and C16, which work together to reduce ripple and provide a clean 1.25 V DC output. This lower voltage is typically used to power memory devices that require a reduced voltage level.

Overall, the design of the NCP5201 chip exemplifies the integration of multiple power management functions into a single component, allowing for compact and efficient circuit designs in electronic applications.Having two sets of PWM signal generating circuit within NCP5201 chip, a set of output pins and the feet two opposite phase PWM signal, respectively applied to the gates of the three field effect transistor, the field effect transistor so that two sets are alternately turned on the battery supply voltage into a pulse voltage, then by L2, COUT filter becomes +2.5 V voltage supply for the memory. At the same time, + 2.5 V power supply is applied to the chip @ foot inside the chip provided with a second set PWM signal generating circuit and two field-effect transistors.

The two field effect transistors of the voltage of 2.5 V into a pulse signal, pin output by the chip, the C14, c15, C16 after filtered output DC voltage 1.25 V, power the circuit memory.

The NCP5201 is designed to efficiently manage power conversion through the use of pulse width modulation (PWM) techniques. The chip operates by generating two sets of PWM signals that are out of phase, allowing for efficient control of the field effect transistors (FETs). The alternating operation of the FETs ensures that the battery supply voltage is effectively transformed into a pulsed output, which is crucial for applications that require a stable voltage supply.

In the first stage, the PWM signals control the gates of the FETs, enabling them to switch on and off rapidly. This switching action is what allows the circuit to convert the DC battery voltage into a pulsed output. The inductor L2 and capacitor COUT play a vital role in smoothing out the pulsed voltage, resulting in a stable +2.5 V output. This voltage is essential for the operation of memory circuits, which often require a specific voltage level for optimal performance.

Furthermore, the internal circuitry of the NCP5201 utilizes the +2.5 V supply to power a second PWM generation circuit. This circuit operates similarly to the first, utilizing two additional FETs to produce another pulsed output signal. The output from this second stage is filtered through capacitors C14, C15, and C16, which work together to reduce ripple and provide a clean 1.25 V DC output. This lower voltage is typically used to power memory devices that require a reduced voltage level.

Overall, the design of the NCP5201 chip exemplifies the integration of multiple power management functions into a single component, allowing for compact and efficient circuit designs in electronic applications.Having two sets of PWM signal generating circuit within NCP5201 chip, a set of output pins and the feet two opposite phase PWM signal, respectively applied to the gates of the three field effect transistor, the field effect transistor so that two sets are alternately turned on the battery supply voltage into a pulse voltage, then by L2, COUT filter becomes +2.5 V voltage supply for the memory. At the same time, + 2.5 V power supply is applied to the chip @ foot inside the chip provided with a second set PWM signal generating circuit and two field-effect transistors.

The two field effect transistors of the voltage of 2.5 V into a pulse signal, pin output by the chip, the C14, c15, C16 after filtered output DC voltage 1.25 V, power the circuit memory.