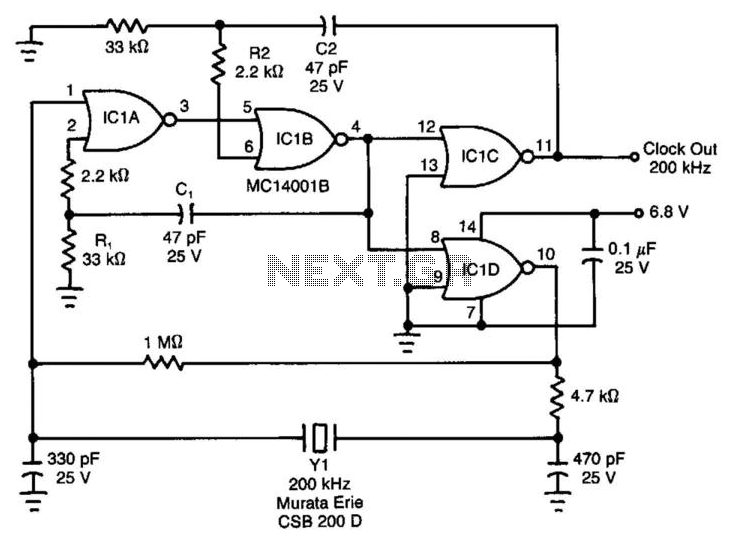

Micropower Clock

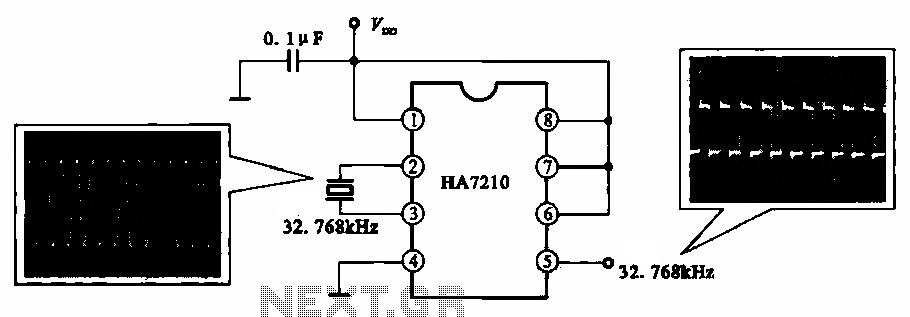

Ceramic resonators are suitable for low-power, low-frequency clock sources, despite their 30-ppm temperature coefficient. However, they exhibit troublesome spurious-resonance modes. This circuit effectively rejects all but the fundamental mode of the resonator. The clock circuit operates within a temperature range of -40 to +80°C and has a power consumption of only 2.8 mW. The rising edge of resonator Y1 triggers a low state in IC1A. Positive feedback, which is AC-coupled from IC1D through CI and RI, confirms this state change at IC1B, ensuring that Miller loading, harmonic components, or minimum rise times at IC1A do not cause IC1C to revert to its previous state. This method is also applied to the falling edge of resonator Y1, as IC1C, through C2 and R2, maintains a high state at IC1B. The time constants for IC1, R2, and C2 should be equal and set between 60% to 75% of half the clock's period. Ceramic capacitors with 10% tolerance and X7R dielectric are recommended. These time constants ensure that the logic remains locked and unavailable to the ceramic resonator until just before it transitions legitimately. IC1D and IC1C are configured in parallel to isolate the resonator from external loads and, crucially, from C2.

The described circuit utilizes a ceramic resonator as a clock source, which is advantageous for applications requiring low power consumption and low frequency. The design addresses the challenges posed by spurious resonance modes, which can interfere with the clock signal's integrity. By implementing a feedback mechanism, the circuit ensures that only the fundamental frequency of the resonator is utilized, enhancing stability and performance.

The circuit operates effectively across a wide temperature range, which is essential for applications in varying environmental conditions. The low power consumption of 2.8 mW makes it suitable for battery-operated devices, extending their operational life.

The arrangement of ICs within the circuit is critical. IC1A, IC1B, IC1C, and IC1D work in conjunction to create a robust feedback loop. The toggling action initiated by the rising edge of the resonator is reinforced by the AC-coupled feedback from IC1D, which prevents unwanted state changes that could be caused by external factors. This design feature is particularly important in maintaining the reliability of the clock signal.

The time constants associated with R2 and C2 are crucial in determining the response time of the circuit. By selecting values that constitute 60% to 75% of half the clock period, the design ensures that the circuit remains in a stable state until a valid transition is imminent. The choice of ceramic capacitors with a specific dielectric type ensures minimal variation in capacitance with temperature, further stabilizing the circuit's operation.

The parallel configuration of IC1D and IC1C serves to isolate the resonator from external influences, which is vital for maintaining signal integrity. This isolation prevents loading effects from external circuits that could distort the clock signal, thereby enhancing the overall performance of the system.

In summary, the circuit effectively leverages the properties of ceramic resonators while mitigating their drawbacks, resulting in a reliable and efficient clock source suitable for various low-power applications. Although ceramic resonators are a good choice for low-power, low-frequency clock sources (if you can stand their 30-ppm te mperature coefficient), they have troublesome, spurious-resonance modes. This circuit rejects all but the resonator"s fundamental mode. This clock circuit works from -40 to +80°C and consumes only 2.8 mW. The rising edge of resonator Y1 toggles IC1A low. ac-coupled positive feedback from IC1D via CI and RI immediately confirms this state change at IC1B so that Miller loading, harmonic components, or below-minimum rise times at IC1A cannot force IC1C to relapse to its previous state. This tactic also applies to resonator Yl"s falling edge because IC1C, via C2 and R2, holds IC1B high.

Choose time constants iiCi, and R2C2 to be equal and ranging from 60 to 75% of one-half of the clock"s period. Ceramic capacitors (10% tolerance) with X7R dielectric work well. With these time constants, the logic will be locked and unavailable to the ceramic resonator until just before it executes a legitimate transition.

IC1D and IC1C are in parallel to isolate the resonator from external loads and, more importantly, from C2.

The described circuit utilizes a ceramic resonator as a clock source, which is advantageous for applications requiring low power consumption and low frequency. The design addresses the challenges posed by spurious resonance modes, which can interfere with the clock signal's integrity. By implementing a feedback mechanism, the circuit ensures that only the fundamental frequency of the resonator is utilized, enhancing stability and performance.

The circuit operates effectively across a wide temperature range, which is essential for applications in varying environmental conditions. The low power consumption of 2.8 mW makes it suitable for battery-operated devices, extending their operational life.

The arrangement of ICs within the circuit is critical. IC1A, IC1B, IC1C, and IC1D work in conjunction to create a robust feedback loop. The toggling action initiated by the rising edge of the resonator is reinforced by the AC-coupled feedback from IC1D, which prevents unwanted state changes that could be caused by external factors. This design feature is particularly important in maintaining the reliability of the clock signal.

The time constants associated with R2 and C2 are crucial in determining the response time of the circuit. By selecting values that constitute 60% to 75% of half the clock period, the design ensures that the circuit remains in a stable state until a valid transition is imminent. The choice of ceramic capacitors with a specific dielectric type ensures minimal variation in capacitance with temperature, further stabilizing the circuit's operation.

The parallel configuration of IC1D and IC1C serves to isolate the resonator from external influences, which is vital for maintaining signal integrity. This isolation prevents loading effects from external circuits that could distort the clock signal, thereby enhancing the overall performance of the system.

In summary, the circuit effectively leverages the properties of ceramic resonators while mitigating their drawbacks, resulting in a reliable and efficient clock source suitable for various low-power applications. Although ceramic resonators are a good choice for low-power, low-frequency clock sources (if you can stand their 30-ppm te mperature coefficient), they have troublesome, spurious-resonance modes. This circuit rejects all but the resonator"s fundamental mode. This clock circuit works from -40 to +80°C and consumes only 2.8 mW. The rising edge of resonator Y1 toggles IC1A low. ac-coupled positive feedback from IC1D via CI and RI immediately confirms this state change at IC1B so that Miller loading, harmonic components, or below-minimum rise times at IC1A cannot force IC1C to relapse to its previous state. This tactic also applies to resonator Yl"s falling edge because IC1C, via C2 and R2, holds IC1B high.

Choose time constants iiCi, and R2C2 to be equal and ranging from 60 to 75% of one-half of the clock"s period. Ceramic capacitors (10% tolerance) with X7R dielectric work well. With these time constants, the logic will be locked and unavailable to the ceramic resonator until just before it executes a legitimate transition.

IC1D and IC1C are in parallel to isolate the resonator from external loads and, more importantly, from C2.