mixer translates multiple standards

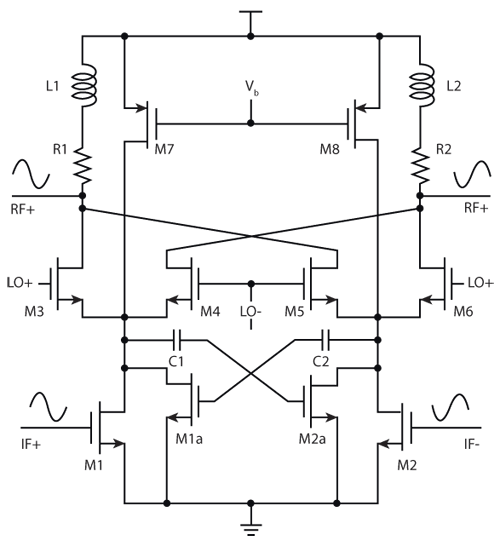

This broadband frequency-upconversion mixer has been simulated with and without a novel linearity-enhancement circuit, making it suitable for multiple-standard wireless applications from 1.0 to 10.6 GHz. Wireless communications products continue to support multiple communications standards, prompting designers to develop components that can operate across various bands and standards. Ideally, a single device would manage all wireless communications standards and bands. However, prior to achieving this goal, it is essential to develop components, such as upconversion mixers, that can function with several wireless standards. By utilizing a cross-coupling post-distortion technique (CCPFT), an upconversion mixer with exceptional linearity for multiple wireless communications standards has been designed. The mixer was simulated using commercial software and is based on fabrication with a CHRT 0.18-µm silicon CMOS mixed-signal/RF semiconductor process. The mixer consumes only 5 mW of power from a +1.2-VDC supply, achieving a maximum input third-order intercept point (IIP3) of +16.56 dBm with a conversion gain of 3.5 dB (flat within ±0.5 dB), and a noise figure of 10.7 dB (also flat within ±0.5 dB) across the frequency range of 1.0 to 10.6 GHz. This performance makes it ideally suited for software-defined radios (SDRs) and multiple-band ultrawideband (UWB) communications systems. An effective upconversion mixer should provide a low noise figure, reasonable gain, and high linearity while consuming low power to be effective in modern multiple-standard wireless transmitters. Several mixers have been developed, including a 3.0-to-5.1-GHz upconversion mixer designed with a current-reuse technique to minimize power consumption, achieving 3.8 dB gain and an 8.4 dB noise figure, but only -7.6 dBm IIP3. Another reference presents a 1.0-to-11.0-GHz upconversion mixer with a folded structure and inductor-free matching network, which achieves +12 dBm IIP3 but with a conversion gain below 0 dB (-6 dB). A 3.0-to-5.0-GHz upconversion mixer with a current-reuse bleeding technique has been reported, achieving 6.5 dB conversion gain and +11.6 dBm IIP3, but it dissipates 11.0 mW and has a complex structure. A 6.0-to-8.0-GHz upconversion mixer using a feedback loop in its transconductance stage achieves 0 dB conversion gain and a 7.0 dB noise figure, though its linearity is not specified. These examples indicate trade-offs between linearity and other performance parameters. To achieve high linearity in upconversion mixers without compromising other key performance metrics, linearization techniques are necessary. Various circuit linearization methods have been developed for low-noise amplifiers (LNAs), with one common approach being the derivative superposition technique, which uses auxiliary transistors biased in weak inversion to produce a nonlinear current that cancels out third-order intermodulation from the main transistors. However, this method is primarily effective at lower frequencies and may introduce additional gate noise. Recently, post-distortion and cross-coupling post-distortion techniques have been implemented for LNA linearization, yielding IIP3 levels exceeding +10 dBm without significantly degrading other key parameters. For multiple-standard wireless communications, a low-voltage upconversion mixer has been developed using a pseudodifferential double-balanced structure, providing high isolation between ports while operating at low supply voltage. It also incorporates a current-bleeding topology to enhance noise and linearity performance. The cross-coupling post-distortion technique has been adopted to further improve IIP3.

The described broadband frequency-upconversion mixer represents a significant advancement in the field of wireless communications, particularly for applications requiring compatibility with multiple standards. The design employs a cross-coupling post-distortion technique, which enhances linearity while maintaining low power consumption, a critical requirement for modern wireless transmitters. The use of a CHRT 0.18-µm silicon CMOS process facilitates integration and miniaturization, making the mixer suitable for compact devices. The achieved specifications, such as a maximum IIP3 of +16.56 dBm and a noise figure of 10.7 dB, demonstrate the device's capability to operate effectively across a broad frequency range. The low power consumption of 5 mW from a +1.2-VDC supply further enhances its appeal for battery-operated devices and energy-efficient systems.

The integration of linearization techniques, such as the cross-coupling post-distortion method, addresses the inherent trade-offs between linearity and other performance metrics, allowing for improved performance in challenging wireless environments. This mixer is particularly beneficial for software-defined radios and ultrawideband communications, where versatility and performance are paramount. The development of such advanced upconversion mixers is essential for the ongoing evolution of wireless communication technologies, enabling devices to meet the demands of diverse applications and communication standards.This broadband frequency-upconversion mixer, which has been simulated with and without a novel linearity-enhancement circuit, is suitable for multiple-standard wireless applications from 1. 0 to 10. 6 GHz. Wireless communications products continue to support multiple communications standards, pushing designers to develop components that can work acr

oss as many bands and standards as possible. Ideally, a single device would handle all wireless communications standards and bands. But before that day comes, it is necessary to develop components ”such as upconversion mixers ”that can operate with several wireless standards. By employing a cross-coupling post-distortion technique (CCPFT), it was possible to design an upconversion mixer with outstanding linearity for multiple wireless communications standards.

The mixer was simulated with commercial software, based on fabrication with a CHRT 0. 18- m silicon CMOS mixed-signal/RF semiconductor process. As will be shown, the mixer consumes only 5 mW power from a +1. 2-VDC supply. It achieves a maximum input third-order intercept point (IIP3) of +16. 56 dBm with 3. 5 dB conversion gain (flat to within ±0. 5 dB), with 10. 7-dB noise figure (flat to within ±0. 5 dB) across a frequency range of 1. 0 to 10. 6 GHz. This makes it ideally suited for software-defined radios (SDRs), as well as multiple-band ultrawideband (UWB) communications systems. 1 An upconversion mixer should provide low noise figure with reasonable gain and high linearity while consuming low power to be effective in modern multiple-standard wireless transmitters.

Such mixers have been developed, including the 3. 0-to-5. 1-GHz upconversion mixer of ref. 2 designed with a current-reuse technique to minimize power consumption. It delivers 3. 8-dB gain and 8. 4-dB noise figure, but only ’7. 6-dBm IIP3. In ref. 3, a 1. 0-to-11. 0-GHz upconversion mixer was proposed, with an adopted fold structure and inductor-free matching network. Although its IIP3 reaches +12 dBm, the conversion gain is below 0 dB ( ’6 dB). In ref. 4, a 3. 0-to-5. 0-GHz upconversion mixer with current-reuse bleeding technique was presented. It achieves 6. 5-dB conversion gain and IIP3 of +11. 6 dBm. However, its power dissipation is 11. 0 mW, and the mixer has a very complicated structure. In ref. 5, a 6. 0-to-8. 0-GHz upconversion mixer was proposed which uses a feedback loop in its transconductance stage. It achieves 0-dB conversion gain and 7. 0 dB noise figure, but its linearity is not mentioned. From these reference examples, it is apparent that tradeoffs were made between linearity and other performance parameters.

For high upconversion-mixer linearity without sacrificing the other key mixer performance parameters, it is necessary to apply some linearization techniques. Numerous circuit linearization techniques have been developed for low-noise amplifiers (LNAs). One commonly used method is the derivative superposition technique. 6, 7 It employs auxiliary transistors biased via weak inversion, which produces a nonlinear current to cancel out the third-order intermodulation generated by the main transistors.

This approach is mainly effective at lower frequencies and can induce additional gate noise. Recently, a post-distortion technique8 and a cross-coupling post-distortion technique9, 10 were implemented for LNA linearization. Both methods yielded IIP3 performance levels exceeding +10 dBm without seriously degrading the other key LNA parameters.

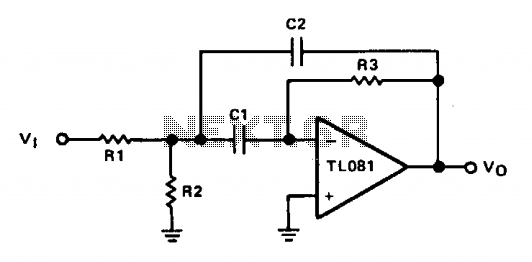

For multiple-standard wireless communications applications, a low-voltage upconversion mixer was developed using a pseudodifferential double-balanced structure, allowing for high isolation between ports while operating with low supply voltage. It also employs a current-bleeding topology for improved noise and linearity performance. 11 A cross-coupling post-distortion technique was also adopted to further improve IIP3. The added linearization circui 🔗 External reference

The described broadband frequency-upconversion mixer represents a significant advancement in the field of wireless communications, particularly for applications requiring compatibility with multiple standards. The design employs a cross-coupling post-distortion technique, which enhances linearity while maintaining low power consumption, a critical requirement for modern wireless transmitters. The use of a CHRT 0.18-µm silicon CMOS process facilitates integration and miniaturization, making the mixer suitable for compact devices. The achieved specifications, such as a maximum IIP3 of +16.56 dBm and a noise figure of 10.7 dB, demonstrate the device's capability to operate effectively across a broad frequency range. The low power consumption of 5 mW from a +1.2-VDC supply further enhances its appeal for battery-operated devices and energy-efficient systems.

The integration of linearization techniques, such as the cross-coupling post-distortion method, addresses the inherent trade-offs between linearity and other performance metrics, allowing for improved performance in challenging wireless environments. This mixer is particularly beneficial for software-defined radios and ultrawideband communications, where versatility and performance are paramount. The development of such advanced upconversion mixers is essential for the ongoing evolution of wireless communication technologies, enabling devices to meet the demands of diverse applications and communication standards.This broadband frequency-upconversion mixer, which has been simulated with and without a novel linearity-enhancement circuit, is suitable for multiple-standard wireless applications from 1. 0 to 10. 6 GHz. Wireless communications products continue to support multiple communications standards, pushing designers to develop components that can work acr

oss as many bands and standards as possible. Ideally, a single device would handle all wireless communications standards and bands. But before that day comes, it is necessary to develop components ”such as upconversion mixers ”that can operate with several wireless standards. By employing a cross-coupling post-distortion technique (CCPFT), it was possible to design an upconversion mixer with outstanding linearity for multiple wireless communications standards.

The mixer was simulated with commercial software, based on fabrication with a CHRT 0. 18- m silicon CMOS mixed-signal/RF semiconductor process. As will be shown, the mixer consumes only 5 mW power from a +1. 2-VDC supply. It achieves a maximum input third-order intercept point (IIP3) of +16. 56 dBm with 3. 5 dB conversion gain (flat to within ±0. 5 dB), with 10. 7-dB noise figure (flat to within ±0. 5 dB) across a frequency range of 1. 0 to 10. 6 GHz. This makes it ideally suited for software-defined radios (SDRs), as well as multiple-band ultrawideband (UWB) communications systems. 1 An upconversion mixer should provide low noise figure with reasonable gain and high linearity while consuming low power to be effective in modern multiple-standard wireless transmitters.

Such mixers have been developed, including the 3. 0-to-5. 1-GHz upconversion mixer of ref. 2 designed with a current-reuse technique to minimize power consumption. It delivers 3. 8-dB gain and 8. 4-dB noise figure, but only ’7. 6-dBm IIP3. In ref. 3, a 1. 0-to-11. 0-GHz upconversion mixer was proposed, with an adopted fold structure and inductor-free matching network. Although its IIP3 reaches +12 dBm, the conversion gain is below 0 dB ( ’6 dB). In ref. 4, a 3. 0-to-5. 0-GHz upconversion mixer with current-reuse bleeding technique was presented. It achieves 6. 5-dB conversion gain and IIP3 of +11. 6 dBm. However, its power dissipation is 11. 0 mW, and the mixer has a very complicated structure. In ref. 5, a 6. 0-to-8. 0-GHz upconversion mixer was proposed which uses a feedback loop in its transconductance stage. It achieves 0-dB conversion gain and 7. 0 dB noise figure, but its linearity is not mentioned. From these reference examples, it is apparent that tradeoffs were made between linearity and other performance parameters.

For high upconversion-mixer linearity without sacrificing the other key mixer performance parameters, it is necessary to apply some linearization techniques. Numerous circuit linearization techniques have been developed for low-noise amplifiers (LNAs). One commonly used method is the derivative superposition technique. 6, 7 It employs auxiliary transistors biased via weak inversion, which produces a nonlinear current to cancel out the third-order intermodulation generated by the main transistors.

This approach is mainly effective at lower frequencies and can induce additional gate noise. Recently, a post-distortion technique8 and a cross-coupling post-distortion technique9, 10 were implemented for LNA linearization. Both methods yielded IIP3 performance levels exceeding +10 dBm without seriously degrading the other key LNA parameters.

For multiple-standard wireless communications applications, a low-voltage upconversion mixer was developed using a pseudodifferential double-balanced structure, allowing for high isolation between ports while operating with low supply voltage. It also employs a current-bleeding topology for improved noise and linearity performance. 11 A cross-coupling post-distortion technique was also adopted to further improve IIP3. The added linearization circui 🔗 External reference