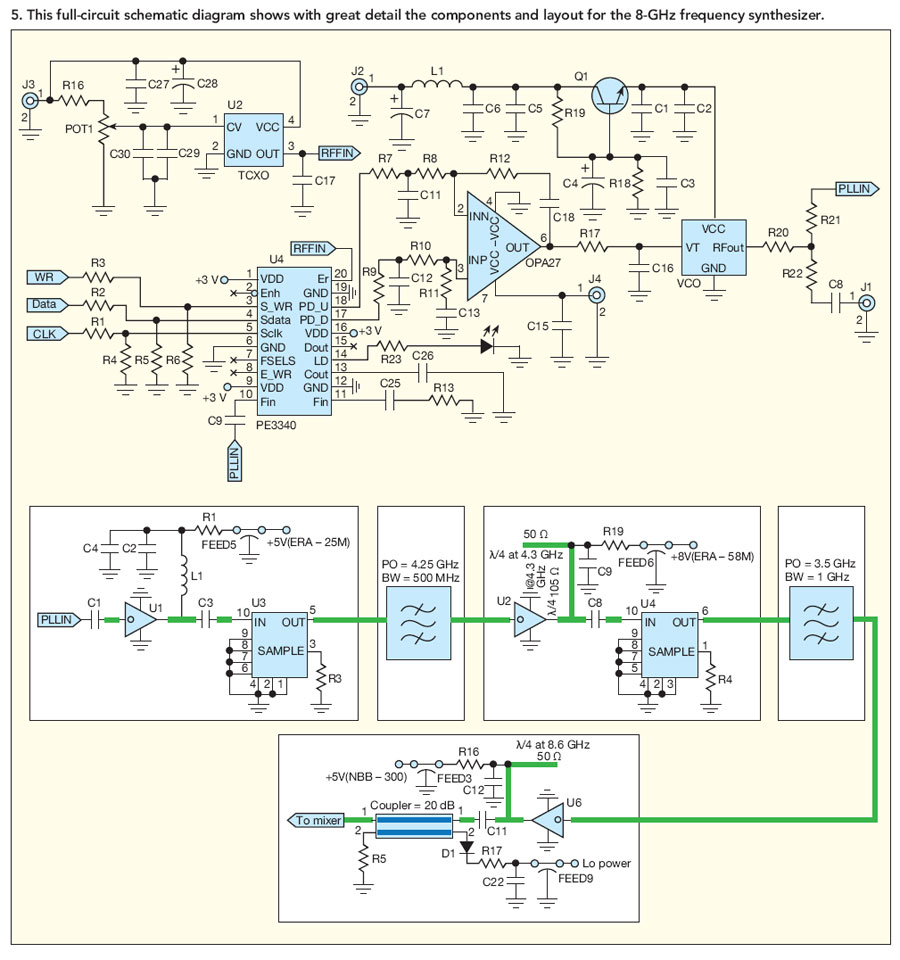

optimizing pll performance levels

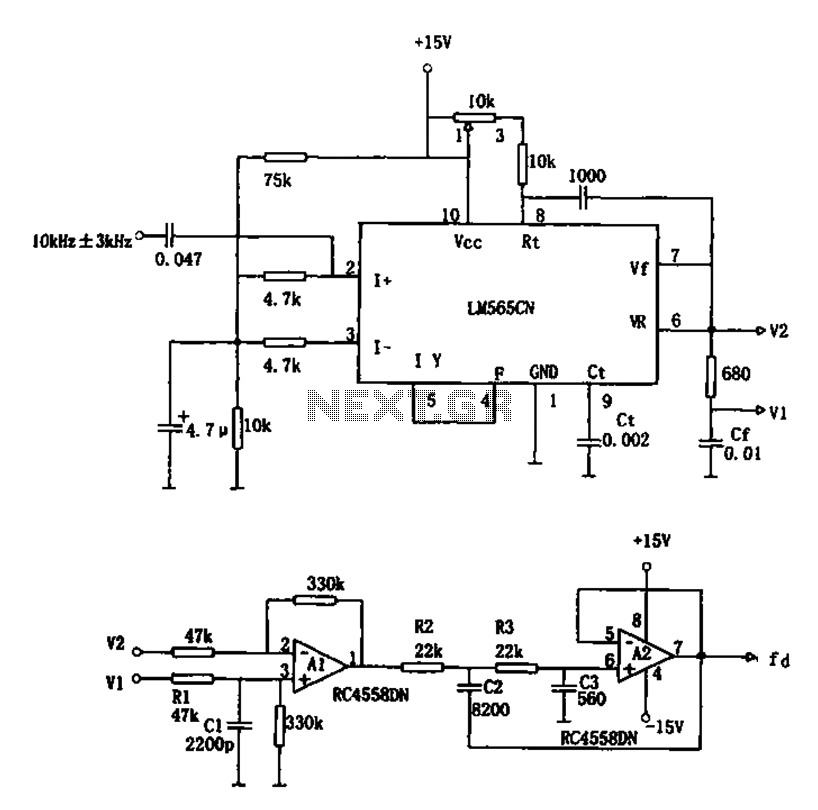

Designing a Phase-Locked Loop (PLL) synthesizer for modern mobile communication systems requires achieving the right balance among several trade-offs, including spurious levels and frequency switching speed.

The design of a Phase-Locked Loop synthesizer for mobile communication systems is a critical task that necessitates careful consideration of various performance parameters. The PLL synthesizer serves as a key component in frequency generation, allowing for the precise control of output frequencies that are essential for effective communication.

One of the primary challenges in PLL design is managing spurious levels, which are unwanted signals that can interfere with the desired output. These spurious signals can arise from various sources, including non-linearities in the components, power supply noise, and insufficient filtering. Therefore, careful selection of components, such as low-noise amplifiers and high-quality passive filters, is essential to minimize these unwanted signals.

Another critical factor is the frequency switching speed, which refers to how quickly the synthesizer can change its output frequency in response to varying communication needs. This is particularly important in mobile communications, where rapid changes in frequency are often required to maintain a stable connection as the device moves between different cell towers. The design must include a fast phase detector and a loop filter that can respond quickly to changes in the input signal, ensuring that the PLL can lock onto new frequencies without significant delay.

Additionally, the PLL's loop bandwidth must be optimized to balance stability and response time. A wider loop bandwidth can improve the speed of frequency acquisition but may increase susceptibility to noise, while a narrower bandwidth can enhance noise performance but slow down frequency switching. Thus, the designer must carefully analyze the specific requirements of the communication system to determine the optimal loop bandwidth.

Overall, designing a PLL synthesizer for mobile communications involves a comprehensive approach that addresses spurious levels, frequency switching speed, and loop bandwidth, ensuring that the synthesizer meets the demanding performance criteria of modern communication systems.Designing a PLL synthesizer for modern mobile communications systems involves achieving the proper balance among a number of tradeoffs, including spurious levels and frequency switching speed.. 🔗 External reference

The design of a Phase-Locked Loop synthesizer for mobile communication systems is a critical task that necessitates careful consideration of various performance parameters. The PLL synthesizer serves as a key component in frequency generation, allowing for the precise control of output frequencies that are essential for effective communication.

One of the primary challenges in PLL design is managing spurious levels, which are unwanted signals that can interfere with the desired output. These spurious signals can arise from various sources, including non-linearities in the components, power supply noise, and insufficient filtering. Therefore, careful selection of components, such as low-noise amplifiers and high-quality passive filters, is essential to minimize these unwanted signals.

Another critical factor is the frequency switching speed, which refers to how quickly the synthesizer can change its output frequency in response to varying communication needs. This is particularly important in mobile communications, where rapid changes in frequency are often required to maintain a stable connection as the device moves between different cell towers. The design must include a fast phase detector and a loop filter that can respond quickly to changes in the input signal, ensuring that the PLL can lock onto new frequencies without significant delay.

Additionally, the PLL's loop bandwidth must be optimized to balance stability and response time. A wider loop bandwidth can improve the speed of frequency acquisition but may increase susceptibility to noise, while a narrower bandwidth can enhance noise performance but slow down frequency switching. Thus, the designer must carefully analyze the specific requirements of the communication system to determine the optimal loop bandwidth.

Overall, designing a PLL synthesizer for mobile communications involves a comprehensive approach that addresses spurious levels, frequency switching speed, and loop bandwidth, ensuring that the synthesizer meets the demanding performance criteria of modern communication systems.Designing a PLL synthesizer for modern mobile communications systems involves achieving the proper balance among a number of tradeoffs, including spurious levels and frequency switching speed.. 🔗 External reference