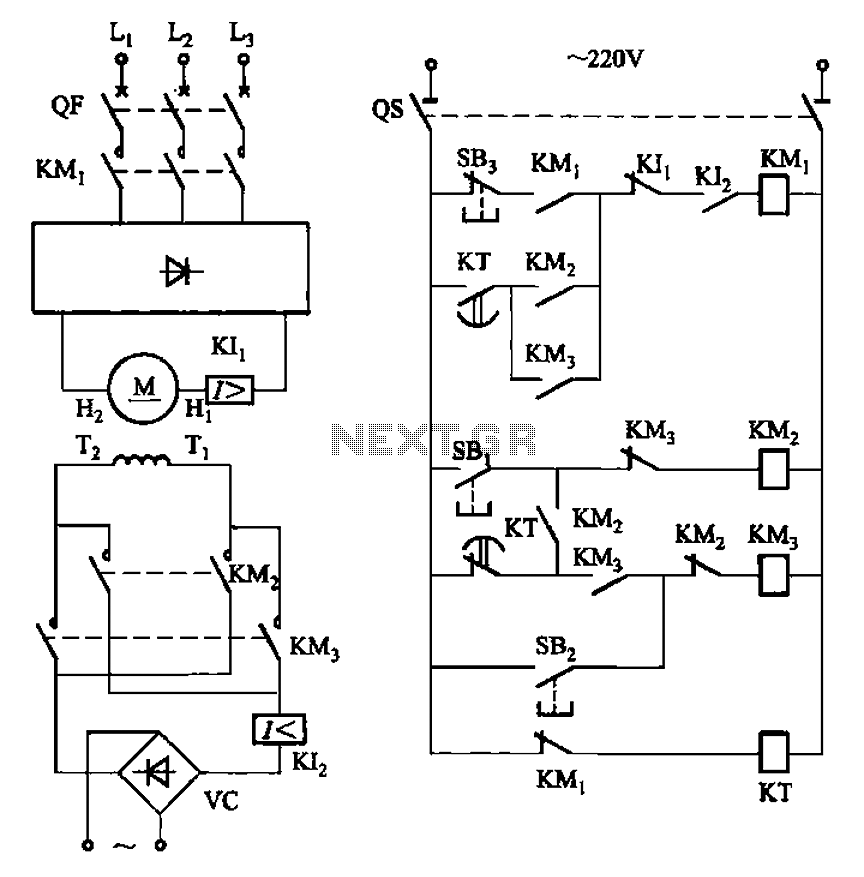

pll circuit

This page will be updated as material becomes available. This new system will essentially replace the original BCD design, which was created by WB6IGP and N6IZW and was featured in the ARRL UHF/Microwave Project Manual. Their work was later revised by WA6CGR. This new design eliminates many shortcomings of the BCD divider chips and implements three PLL circuits that are extremely clean up to and including 47 GHz. One significant advantage of this system is the ability to select any divisor factor appropriate for any crystal frequency, for example, 94.666667 MHz, to cite one example only.

The proposed electronic schematic outlines a modernized system intended to supersede the previous BCD design, addressing its limitations while enhancing performance. The design integrates three Phase-Locked Loop (PLL) circuits, which are critical for achieving stable frequency outputs across a wide range of frequencies, up to 47 GHz. PLL circuits are known for their ability to lock onto a reference frequency and maintain a precise output frequency, making them ideal for high-frequency applications.

The architecture of the new system allows for flexible divisor factor selection, accommodating various crystal oscillator frequencies. This adaptability is particularly advantageous in applications where specific frequency outputs are required. For instance, the design can efficiently handle a crystal frequency of 94.666667 MHz, showcasing its versatility.

The elimination of the shortcomings associated with the original BCD divider chips is a focal point of this design. The previous chips often suffered from issues such as noise, drift, and limited frequency range, which could compromise overall system performance. By utilizing advanced PLL circuits, the new design aims to provide a more robust solution with improved signal integrity and reduced phase noise.

In summary, the updated system represents a significant advancement in frequency division technology, enhancing both performance and flexibility for applications in the UHF and microwave frequency ranges. The implementation of three PLL circuits, coupled with the ability to select appropriate divisor factors, positions this design as a superior alternative to its predecessors.This page will be updated as Material becomes available. This New System will essentially replace the original BCD Design originally designed by WB6IGP and N6IZW and appeared in ARRL UHF/Microwave Project Manual. Their efforts were later revised by WA6CGR. This New Design eliminates the many short Falls of the BCD Divider Chips and Implements actu ally 3 PLL Circuits that are extremely clean up to and including 47Ghz. One Huge advantage of this System is the ability to select any divisor factor appropriate for any XTAL Freq. i. e. 94. 666667Mhz to sight one example only. 🔗 External reference

The proposed electronic schematic outlines a modernized system intended to supersede the previous BCD design, addressing its limitations while enhancing performance. The design integrates three Phase-Locked Loop (PLL) circuits, which are critical for achieving stable frequency outputs across a wide range of frequencies, up to 47 GHz. PLL circuits are known for their ability to lock onto a reference frequency and maintain a precise output frequency, making them ideal for high-frequency applications.

The architecture of the new system allows for flexible divisor factor selection, accommodating various crystal oscillator frequencies. This adaptability is particularly advantageous in applications where specific frequency outputs are required. For instance, the design can efficiently handle a crystal frequency of 94.666667 MHz, showcasing its versatility.

The elimination of the shortcomings associated with the original BCD divider chips is a focal point of this design. The previous chips often suffered from issues such as noise, drift, and limited frequency range, which could compromise overall system performance. By utilizing advanced PLL circuits, the new design aims to provide a more robust solution with improved signal integrity and reduced phase noise.

In summary, the updated system represents a significant advancement in frequency division technology, enhancing both performance and flexibility for applications in the UHF and microwave frequency ranges. The implementation of three PLL circuits, coupled with the ability to select appropriate divisor factors, positions this design as a superior alternative to its predecessors.This page will be updated as Material becomes available. This New System will essentially replace the original BCD Design originally designed by WB6IGP and N6IZW and appeared in ARRL UHF/Microwave Project Manual. Their efforts were later revised by WA6CGR. This New Design eliminates the many short Falls of the BCD Divider Chips and Implements actu ally 3 PLL Circuits that are extremely clean up to and including 47Ghz. One Huge advantage of this System is the ability to select any divisor factor appropriate for any XTAL Freq. i. e. 94. 666667Mhz to sight one example only. 🔗 External reference