PLL Lock Detection

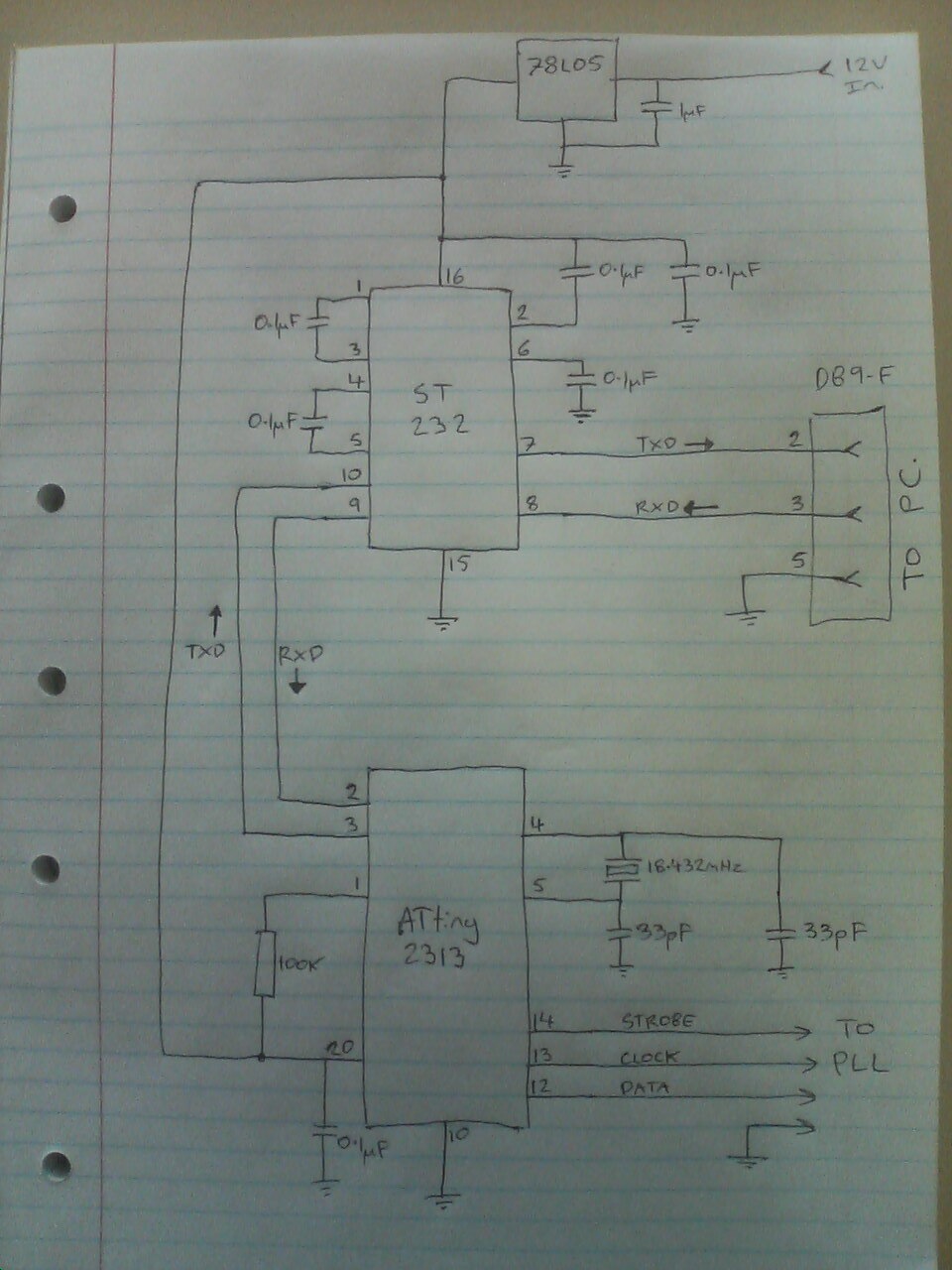

In certain Phase-Locked Loop (PLL) applications, it is often necessary to provide a lock indication when the PLL is in a locked state. The simplest method for this indication is a binary signal, represented as either 0 or 1.

In PLL circuits, a lock indication serves as an essential feedback mechanism, confirming that the output frequency of the voltage-controlled oscillator (VCO) is synchronized with the reference frequency. This synchronization is crucial for ensuring that the PLL operates correctly and that the output signal meets the desired specifications.

To implement a binary lock indication, a simple logic circuit can be employed. This circuit typically consists of a comparator that monitors the phase difference between the reference signal and the VCO output. When the phase difference falls within an acceptable range—indicating that the PLL is locked—the comparator outputs a high signal (1). Conversely, if the PLL is not locked, the output will be low (0).

In practical applications, the binary output can be used to drive an LED indicator, which visually represents the lock status. Additionally, this signal can be interfaced with microcontrollers, allowing for further processing or integration into larger systems.

For more sophisticated applications, additional indicators may be incorporated, such as a multi-state LED or a graphical display, which can provide more detailed information about the PLL's performance, including lock time and phase error. However, for basic applications, the binary indication remains a straightforward and effective solution to signal the locked state of a PLL.In some PLL application, sometimes we need to provide lock indication when the PLL is in locked state. The simplest one is binary indication, 0 or 1 to. 🔗 External reference

In PLL circuits, a lock indication serves as an essential feedback mechanism, confirming that the output frequency of the voltage-controlled oscillator (VCO) is synchronized with the reference frequency. This synchronization is crucial for ensuring that the PLL operates correctly and that the output signal meets the desired specifications.

To implement a binary lock indication, a simple logic circuit can be employed. This circuit typically consists of a comparator that monitors the phase difference between the reference signal and the VCO output. When the phase difference falls within an acceptable range—indicating that the PLL is locked—the comparator outputs a high signal (1). Conversely, if the PLL is not locked, the output will be low (0).

In practical applications, the binary output can be used to drive an LED indicator, which visually represents the lock status. Additionally, this signal can be interfaced with microcontrollers, allowing for further processing or integration into larger systems.

For more sophisticated applications, additional indicators may be incorporated, such as a multi-state LED or a graphical display, which can provide more detailed information about the PLL's performance, including lock time and phase error. However, for basic applications, the binary indication remains a straightforward and effective solution to signal the locked state of a PLL.In some PLL application, sometimes we need to provide lock indication when the PLL is in locked state. The simplest one is binary indication, 0 or 1 to. 🔗 External reference