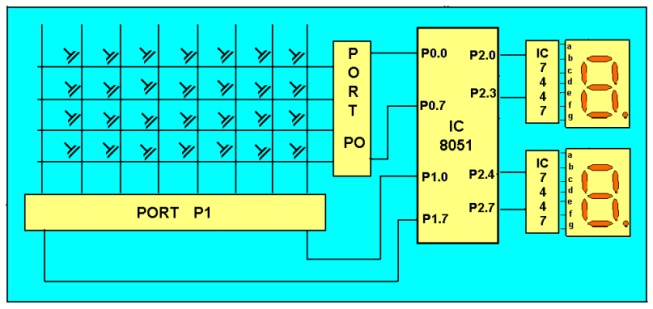

Programable Board with 32K RAM

While there is a list of features that I would like to add (32k EEPROM support, line numbers to 65,535, more stack space, strings, arrays, 16 bit variables and arithmetic, possibly named variables and REM statements for starters), I have not been able to dedicate much time to this project. You are invited to make enhancements, and I sure would like a copy if you make any enhancements. This is the current state of a work in progress, though progress may be slow, I've modified the program memory to use 32k bytes of external RAM. I used a Cypress CY7C199-150, though other 32K static RAMs can be used as well. Just make sure to check the Write and Read pulse polarity on the alternate chip.

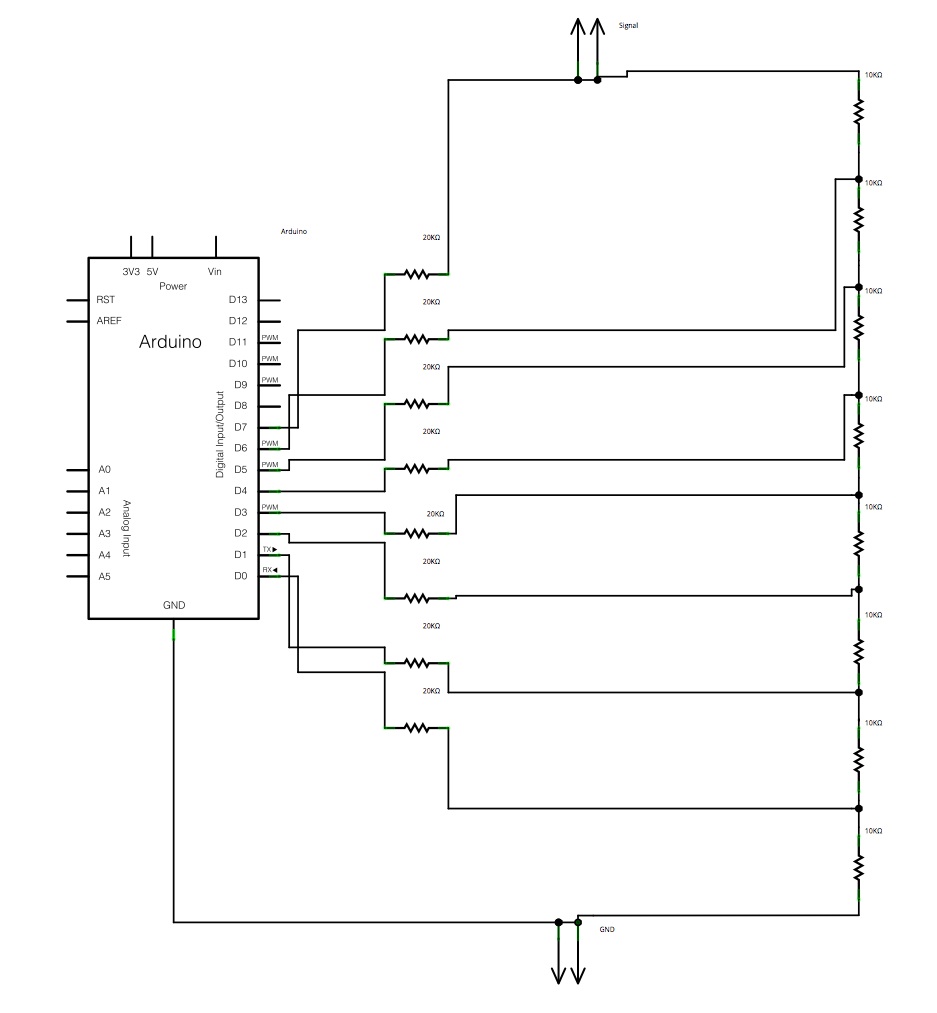

More: The only components necessary to extend the RAM are a 32k static RAM chip, an octal latch for some of the address bits, and the necessary decoupling capacitors. The 0.33 µF caps I used are tantalum, and the RAM I used has 150 ns access time. In the schematic above, I connected any address line from the controller or the latch to any address line on the RAM chip. Similarly, any data line from the controller can connect to any data line on the RAM chip. This makes wiring of the board (or layout of the PCB) simpler than trying to connect corresponding address and data lines.

The circuit described involves the integration of a 32k static RAM chip, specifically the Cypress CY7C199-150, into an existing system to enhance memory capabilities. The primary objective is to expand the program memory to accommodate additional features such as EEPROM support, increased stack space, and advanced data types including strings and arrays. The implementation requires an octal latch to manage address lines effectively.

The design incorporates decoupling capacitors, specifically 0.33 µF tantalum capacitors, to ensure stable operation by filtering out noise and providing a stable power supply to the RAM chip. The access time of the chosen RAM chip is 150 ns, which should be compatible with most microcontroller operations, provided that the timing specifications of the microcontroller are also adhered to.

In terms of connections, the schematic allows for any address line from the controller or the latch to be connected to any address line on the RAM chip. This flexibility simplifies the PCB layout and wiring, as it eliminates the need for strict correspondence between specific address and data lines. Similarly, data lines from the controller can be routed to any data line on the RAM chip, further streamlining the design process.

It is crucial to verify the write and read pulse polarity when using alternative 32K static RAM chips to ensure proper functionality. This consideration is vital for maintaining the integrity of data transactions between the controller and the RAM. Overall, this circuit design provides a robust foundation for extending memory capabilities while allowing for future enhancements in the software and hardware features of the system.While there is a list of features that I would like to add (32k EEPROM support, line numbers to 65,535, more stack space, strings, arrays, 16 bit variables and arithmatic, possibly named variables and REM statements for starters), I have not been able to dedicate much time to this project. You are invited to make enhancements, and I sure would like a copy if you make any enhancements. This is the current stat of a work in progress, though progress may be slow, I've modified the program memory to use 32k bytes of external RAM.

I used a Cypress CY7C199-150, though other 32K static RAMs can be uses as well. Just make sure to check the Write and Read pulse polarity on the alternate chip. The only components necessary to extend the RAM is a 32k static RAM chip, an octal latch for some of the address bits, and the necessary decoupling capacitors. The 0.33 uf caps I used are tanitlum, and the RAM I used has 150 ns access time. In the shematic above, I connected any address line from the controller or the latch to any address line on the RAM chip.

Similarly, any data line from the controller can connect to any data line on the RAM chip. This makes wiring of the board (or layout of the PCB) simpler than trying to connect correspoinding address and data lines. 🔗 External reference

More: The only components necessary to extend the RAM are a 32k static RAM chip, an octal latch for some of the address bits, and the necessary decoupling capacitors. The 0.33 µF caps I used are tantalum, and the RAM I used has 150 ns access time. In the schematic above, I connected any address line from the controller or the latch to any address line on the RAM chip. Similarly, any data line from the controller can connect to any data line on the RAM chip. This makes wiring of the board (or layout of the PCB) simpler than trying to connect corresponding address and data lines.

The circuit described involves the integration of a 32k static RAM chip, specifically the Cypress CY7C199-150, into an existing system to enhance memory capabilities. The primary objective is to expand the program memory to accommodate additional features such as EEPROM support, increased stack space, and advanced data types including strings and arrays. The implementation requires an octal latch to manage address lines effectively.

The design incorporates decoupling capacitors, specifically 0.33 µF tantalum capacitors, to ensure stable operation by filtering out noise and providing a stable power supply to the RAM chip. The access time of the chosen RAM chip is 150 ns, which should be compatible with most microcontroller operations, provided that the timing specifications of the microcontroller are also adhered to.

In terms of connections, the schematic allows for any address line from the controller or the latch to be connected to any address line on the RAM chip. This flexibility simplifies the PCB layout and wiring, as it eliminates the need for strict correspondence between specific address and data lines. Similarly, data lines from the controller can be routed to any data line on the RAM chip, further streamlining the design process.

It is crucial to verify the write and read pulse polarity when using alternative 32K static RAM chips to ensure proper functionality. This consideration is vital for maintaining the integrity of data transactions between the controller and the RAM. Overall, this circuit design provides a robust foundation for extending memory capabilities while allowing for future enhancements in the software and hardware features of the system.While there is a list of features that I would like to add (32k EEPROM support, line numbers to 65,535, more stack space, strings, arrays, 16 bit variables and arithmatic, possibly named variables and REM statements for starters), I have not been able to dedicate much time to this project. You are invited to make enhancements, and I sure would like a copy if you make any enhancements. This is the current stat of a work in progress, though progress may be slow, I've modified the program memory to use 32k bytes of external RAM.

I used a Cypress CY7C199-150, though other 32K static RAMs can be uses as well. Just make sure to check the Write and Read pulse polarity on the alternate chip. The only components necessary to extend the RAM is a 32k static RAM chip, an octal latch for some of the address bits, and the necessary decoupling capacitors. The 0.33 uf caps I used are tanitlum, and the RAM I used has 150 ns access time. In the shematic above, I connected any address line from the controller or the latch to any address line on the RAM chip.

Similarly, any data line from the controller can connect to any data line on the RAM chip. This makes wiring of the board (or layout of the PCB) simpler than trying to connect correspoinding address and data lines. 🔗 External reference