Reset from Multiple Power Supplies

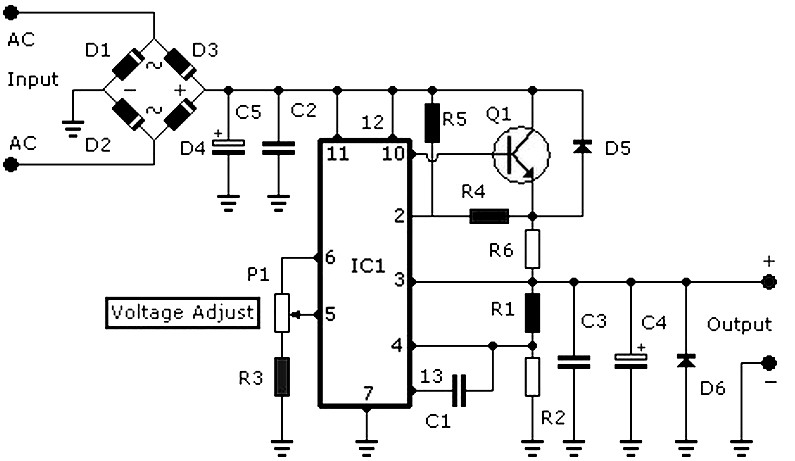

Processor-based systems typically require a voltage supervisor chip to generate a clean reset pulse for the processor whenever a brown-out condition in the power supply is detected. More complex designs that utilize multiple power supplies can become unreliable if some of the supplies are not monitored. The circuit outlined here monitors all the supply rails in the system (specifically +12 V, -12 V, and +5 V) and provides a reset pulse to the processor whenever it detects that any of these are out of tolerance. IC1 (TL7705A) produces a processor reset if the +5 V rail drops below 4.55 V. The capacitor connected to pin 3 determines the reset pulse width (td) according to the formula: td = 12 * CT * 10^3, where CT is in µF, and td is in µs. For instance, a capacitor of 100 nF will generate a reset pulse of approximately 1.2 ms. Pin 6 (RESET) outputs an active-high pulse, while Pin 5 (RESET) outputs an active-low pulse. These outputs are of open collector type, necessitating external pull-down and pull-up resistors, respectively. The RESIN input (Pin 2) of IC1 is driven by two TL7712A supervisors monitoring +12 V (IC2) and -12 V (IC3). The TL7712A generates a reset when the supply voltage drops below a threshold level of 10.8 V. The open collector output RES (Pin 5) of IC2 is connected to the RESIN pin of IC1 and is pulled up to +5 V through a 100 kΩ resistor. The output of IC2 can be directly connected to the reset input of IC1; however, the output of IC3 must be connected via a level shifting device before it can interface with the reset input of IC1, as the output voltage of IC3 can go negative. A JFET transistor (T1) is employed for this level shifting. The JFET turns off when the voltage at its gate-source junction is between 2.5 V and 6 V. When IC3 sends a reset signal, the RES output (pin 6) will drop to ground potential, causing T1 to conduct and trigger a reset of IC1. At all other times, the RES output of IC3 will be pulled to a negative voltage through the 100 kΩ resistor, which stops T1 from conducting and releases the reset. A manual reset push button can also be connected to the RESIN of IC1 if necessary. The SENSE input (Pin 7) of the TL77xx chips is connected to the positive supply rail, while the reference input (pin 1) is equipped with a 100 nF capacitor to mitigate the effects of fast transients.

This circuit design is critical for ensuring reliable operation in processor-based systems, especially in environments where power supply fluctuations are common. The use of the TL7705A voltage supervisor provides a robust mechanism for monitoring the +5 V rail, which is essential for processor functionality. The reset pulse generated by this IC is adjustable through the capacitor at pin 3, allowing for customization based on the specific timing requirements of the application.

The integration of TL7712A supervisors for monitoring the +12 V and -12 V supplies adds a layer of reliability, ensuring that all critical power rails are actively supervised. The open collector configuration of the outputs necessitates careful consideration of pull-up and pull-down resistor values to ensure proper logic levels are maintained during operation.

The level shifting functionality provided by the JFET transistor T1 is particularly noteworthy, as it allows for safe interfacing between different voltage levels, preventing potential damage to the ICs involved. This feature is essential in mixed-voltage systems where components operate at different logic levels.

Overall, this voltage supervision circuit is a well-thought-out design that enhances the reliability of processor-based systems by ensuring that the processor is reset appropriately under brown-out conditions, thereby preventing erratic behavior and potential system failures.Processor based systems usually require a voltage supervisor chip to produce a clean reset pulse to the processor whenever a brown-out` condition of the power supply is detected. More complex designs employing multiple power supplies can be unreliable if some of the supplies are not supervised.

The circuit described here monitors all the supply ra ils in the system (here +12 V, 12 V and +5 V) and provides a reset pulse to the processor whenever it detects any are not within tolerance. IC1 (TL7705A) generates a processor reset if the 5 V rail falls below 4. 55 V. The value of the capacitor fitted to pin 3 defines the reset pulse width td according to the formula: td = 12.

CT 3 103 With CT in µF the value for td is given in µs. A capacitor of 100 nF for example, will produce a reset pulse of around 1. 2 ms. Pin 6 (RESET) outputs an active-high pulse and Pin 5 (RESET) an active-low pulse. The outputs are open collector types so an external pull-down and pull-up resistor (respectively) is required. The RESIN input (Pin 2) of IC1 is driven from two TL7712A supervisors monitoring +12 V (IC2) and 12 V (IC3).

The TL7712A generates a reset when the supply voltage falls below a threshold level of 10. 8 V. The open collector output RES (Pin 5) of IC2 is connected to the RESIN pin of IC1 and pulled up to 5 V via a 100 k resistor. The open collector output of IC2 can be directly connected to the reset input of IC1 but the output of IC3 must be connected via a level shifting device before it can be connected to the reset input of IC1 because the voltage level at the output of IC3 goes negative.

JFET transistor T1 is used to perform the necessary level shifting. The JFET turns off when the voltage at its gate-source junction is between 2. 5 V and 6 V. When IC3 is issuing a reset signal the RES output (pin 6) will go up to ground potential and cause T1 to conduct and trigger a reset of IC1. At all other times the RES output of IC3 will be pulled to a minus voltage via the 100 k resistor which then causes T1 to stop conducting and release the reset.

A manual reset push button can also be connected to RESIN of IC1 if required. The SENSE input (Pin 7) of the TL77xx chips is connected to the positive supply rail. The reference input (pin 1) is fitted with a 100 nF capacitor to reduce the effects of fast transients. 🔗 External reference

This circuit design is critical for ensuring reliable operation in processor-based systems, especially in environments where power supply fluctuations are common. The use of the TL7705A voltage supervisor provides a robust mechanism for monitoring the +5 V rail, which is essential for processor functionality. The reset pulse generated by this IC is adjustable through the capacitor at pin 3, allowing for customization based on the specific timing requirements of the application.

The integration of TL7712A supervisors for monitoring the +12 V and -12 V supplies adds a layer of reliability, ensuring that all critical power rails are actively supervised. The open collector configuration of the outputs necessitates careful consideration of pull-up and pull-down resistor values to ensure proper logic levels are maintained during operation.

The level shifting functionality provided by the JFET transistor T1 is particularly noteworthy, as it allows for safe interfacing between different voltage levels, preventing potential damage to the ICs involved. This feature is essential in mixed-voltage systems where components operate at different logic levels.

Overall, this voltage supervision circuit is a well-thought-out design that enhances the reliability of processor-based systems by ensuring that the processor is reset appropriately under brown-out conditions, thereby preventing erratic behavior and potential system failures.Processor based systems usually require a voltage supervisor chip to produce a clean reset pulse to the processor whenever a brown-out` condition of the power supply is detected. More complex designs employing multiple power supplies can be unreliable if some of the supplies are not supervised.

The circuit described here monitors all the supply ra ils in the system (here +12 V, 12 V and +5 V) and provides a reset pulse to the processor whenever it detects any are not within tolerance. IC1 (TL7705A) generates a processor reset if the 5 V rail falls below 4. 55 V. The value of the capacitor fitted to pin 3 defines the reset pulse width td according to the formula: td = 12.

CT 3 103 With CT in µF the value for td is given in µs. A capacitor of 100 nF for example, will produce a reset pulse of around 1. 2 ms. Pin 6 (RESET) outputs an active-high pulse and Pin 5 (RESET) an active-low pulse. The outputs are open collector types so an external pull-down and pull-up resistor (respectively) is required. The RESIN input (Pin 2) of IC1 is driven from two TL7712A supervisors monitoring +12 V (IC2) and 12 V (IC3).

The TL7712A generates a reset when the supply voltage falls below a threshold level of 10. 8 V. The open collector output RES (Pin 5) of IC2 is connected to the RESIN pin of IC1 and pulled up to 5 V via a 100 k resistor. The open collector output of IC2 can be directly connected to the reset input of IC1 but the output of IC3 must be connected via a level shifting device before it can be connected to the reset input of IC1 because the voltage level at the output of IC3 goes negative.

JFET transistor T1 is used to perform the necessary level shifting. The JFET turns off when the voltage at its gate-source junction is between 2. 5 V and 6 V. When IC3 is issuing a reset signal the RES output (pin 6) will go up to ground potential and cause T1 to conduct and trigger a reset of IC1. At all other times the RES output of IC3 will be pulled to a minus voltage via the 100 k resistor which then causes T1 to stop conducting and release the reset.

A manual reset push button can also be connected to RESIN of IC1 if required. The SENSE input (Pin 7) of the TL77xx chips is connected to the positive supply rail. The reference input (pin 1) is fitted with a 100 nF capacitor to reduce the effects of fast transients. 🔗 External reference