Sawtooth generator circuit a

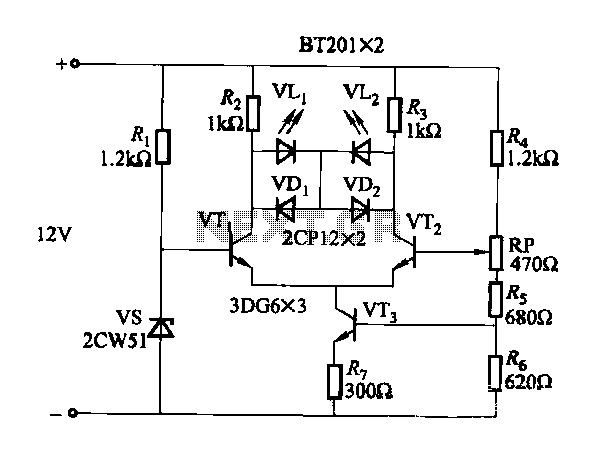

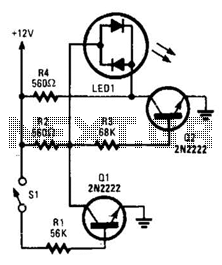

The application circuit depicted is a complementary sawtooth generator. In the schematic, VT1 is the transistor with a base current limiting resistor, which prevents excessive base current flow through the crystal tube. The resistor R4 acts as a bleeder for the collector leakage current of transistor VT2, ensuring that when VT2 turns off, VT1 reliably cuts off as well. Under normal conditions, the power supply is active. When the power is disconnected, the capacitor C is uncharged, resulting in a zero voltage across its terminals (U0 = 0). Consequently, the emitter potential of transistor VT2 is also zero, while the base potential is at point A, leading to UA being greater than UE. This condition turns off transistor VT2. As there is no current surge to the base of VT1, it remains in the off state as well. The power capacitor C charges through the resistor Rs, and as the charging time increases, the potential at point E rises. When the potential at point E exceeds the potential at point A, transistor VT2 enters the active region, allowing collector current to flow through resistor R3 to the base of VT1. This causes VT1 to turn on and also enter the active region. The collector current from VT2 further amplifies the base current of VT1, resulting in positive feedback that drives both VT1 and VT2 into saturation. The capacitor C discharges through the saturated transistors VT1 and VT2. As the discharge time increases, the voltage across capacitor C continues to decrease. When the voltage drops to a certain threshold at point E, the base current of transistor VT1 becomes insufficient to maintain saturation, leading to the circuit turning off due to positive feedback from VT2. This initiates the next cycle of operation. The output waveform is illustrated.

The complementary sawtooth generator circuit operates by utilizing two transistors (VT1 and VT2) configured in a feedback arrangement to produce a repetitive sawtooth waveform. The circuit's operation begins with the capacitor C in a discharged state, resulting in both transistors being off. As the capacitor charges through resistor Rs, the voltage at point E rises gradually. Once it surpasses the voltage at point A, transistor VT2 turns on, allowing a current path through R3 to the base of VT1. This action causes VT1 to also turn on, creating a feedback loop that drives both transistors into saturation.

The saturation of VT1 and VT2 allows the capacitor C to discharge rapidly, generating the downward slope of the sawtooth waveform. The discharge continues until the voltage across capacitor C falls below a critical value. At this point, the feedback mechanism ceases to maintain the saturation of VT1, and both transistors turn off, ceasing the discharge process. The cycle then repeats as the capacitor begins to charge again.

The choice of component values, including the resistors (R3, R4, and Rs) and the capacitor (C), is crucial for determining the frequency and amplitude of the output waveform. The timing characteristics of the sawtooth waveform can be adjusted by varying these component values. The circuit's design allows for stable operation and reliable waveform generation, making it suitable for applications requiring a sawtooth signal, such as in oscillators, waveform generators, and timing circuits.Application circuit is shown in a complementary sawtooth generator. In the figure, the horse is VT1 base current limiting resistor, the conduction time to prevent excessive bas e current flows through the crystal tube VT1 base, R4 transistor VT2 collector leakage current bleeder resistor to ensure when VT2 end, VT1 reliable cutoff. One under normal circumstances, the power island EJ. When the power is Shu Yi cut turned from no charge in the capacitor C, so both ends of the electric voltage is zero (U0-0), then transistor VT2, the emitter potential is zero, the base potential is A potential point, so UA UE.

Transistor VT2 off. VT1 base also granted without electricity surges, also in an off state. Power capacitor C is charged through the resistor Rs, with the increase in charging time, E point potential has also been on the rise. When the potential at the point E over A point potential, VT2 into the enlarged area, its collector current flows through the resistor R3 VT1 base, VT1 from the same cut-off and into the enlarged area, the collector current through the VT1 VT2 amplified again VT2 feedback to the base, so that the result of positive feedback, forcing VT1, VT2 are saturated.

Capacitor C by saturated transistor VT1, VT2 discharge. With the increase of the discharge time, the voltage of the capacitor C continues to decrease. When the voltage drops to a certain point value E, if the parameters chosen, this time, the base current of transistor VT1 VT1 is not sufficient to maintain saturation, will turn off the circuit by making VT2 positive feedback form for off state, circuit into the second cycle. The output waveform is shown

The complementary sawtooth generator circuit operates by utilizing two transistors (VT1 and VT2) configured in a feedback arrangement to produce a repetitive sawtooth waveform. The circuit's operation begins with the capacitor C in a discharged state, resulting in both transistors being off. As the capacitor charges through resistor Rs, the voltage at point E rises gradually. Once it surpasses the voltage at point A, transistor VT2 turns on, allowing a current path through R3 to the base of VT1. This action causes VT1 to also turn on, creating a feedback loop that drives both transistors into saturation.

The saturation of VT1 and VT2 allows the capacitor C to discharge rapidly, generating the downward slope of the sawtooth waveform. The discharge continues until the voltage across capacitor C falls below a critical value. At this point, the feedback mechanism ceases to maintain the saturation of VT1, and both transistors turn off, ceasing the discharge process. The cycle then repeats as the capacitor begins to charge again.

The choice of component values, including the resistors (R3, R4, and Rs) and the capacitor (C), is crucial for determining the frequency and amplitude of the output waveform. The timing characteristics of the sawtooth waveform can be adjusted by varying these component values. The circuit's design allows for stable operation and reliable waveform generation, making it suitable for applications requiring a sawtooth signal, such as in oscillators, waveform generators, and timing circuits.Application circuit is shown in a complementary sawtooth generator. In the figure, the horse is VT1 base current limiting resistor, the conduction time to prevent excessive bas e current flows through the crystal tube VT1 base, R4 transistor VT2 collector leakage current bleeder resistor to ensure when VT2 end, VT1 reliable cutoff. One under normal circumstances, the power island EJ. When the power is Shu Yi cut turned from no charge in the capacitor C, so both ends of the electric voltage is zero (U0-0), then transistor VT2, the emitter potential is zero, the base potential is A potential point, so UA UE.

Transistor VT2 off. VT1 base also granted without electricity surges, also in an off state. Power capacitor C is charged through the resistor Rs, with the increase in charging time, E point potential has also been on the rise. When the potential at the point E over A point potential, VT2 into the enlarged area, its collector current flows through the resistor R3 VT1 base, VT1 from the same cut-off and into the enlarged area, the collector current through the VT1 VT2 amplified again VT2 feedback to the base, so that the result of positive feedback, forcing VT1, VT2 are saturated.

Capacitor C by saturated transistor VT1, VT2 discharge. With the increase of the discharge time, the voltage of the capacitor C continues to decrease. When the voltage drops to a certain point value E, if the parameters chosen, this time, the base current of transistor VT1 VT1 is not sufficient to maintain saturation, will turn off the circuit by making VT2 positive feedback form for off state, circuit into the second cycle. The output waveform is shown