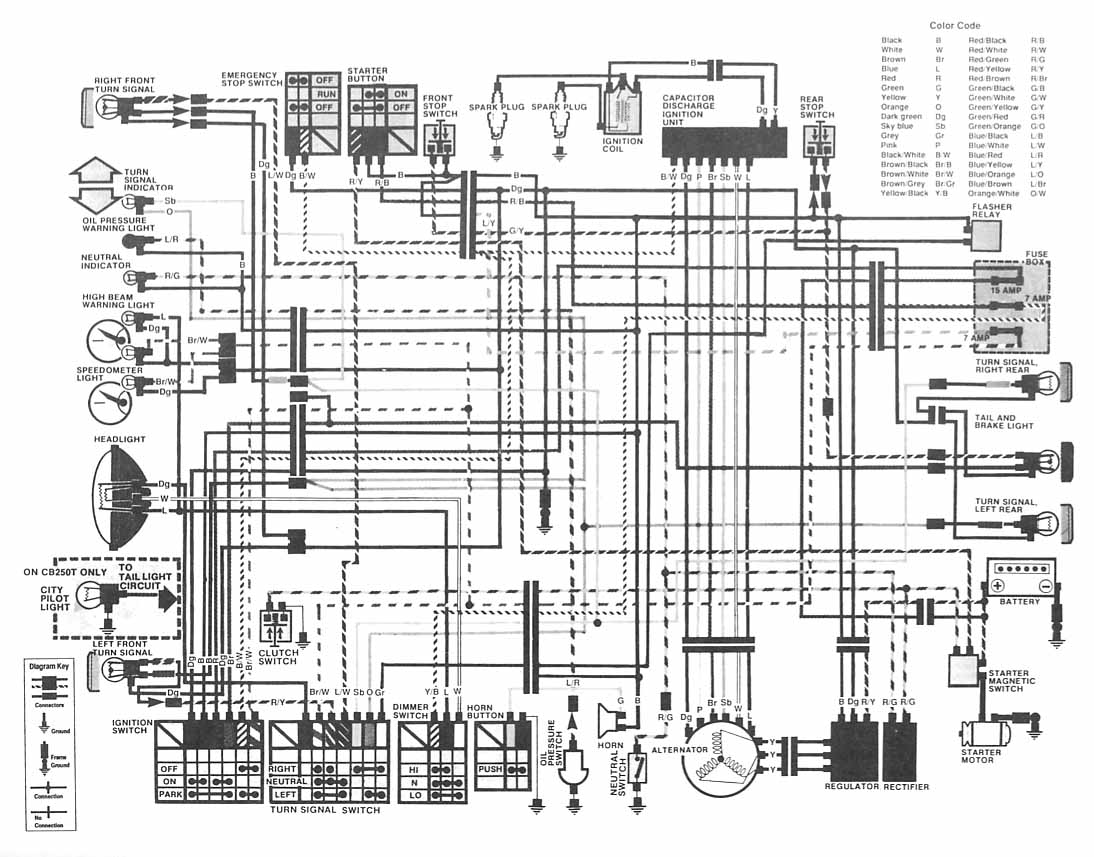

Schematic diagram for OKI/PDG

The layout design of the TIQ Flash ADC closely follows the provided circuit diagram. A row layout is implemented, with rows stacked on top of each other. Each row comprises a comparator, a gain booster, a 0-1 generator, and a ROM (one row).

The TIQ Flash ADC architecture utilizes a specific row-based configuration to optimize performance and efficiency. Each row is designed to facilitate the conversion of an analog signal into a digital representation, which is crucial for high-speed applications. The comparator within each row plays a pivotal role by comparing the input voltage against reference levels, generating a binary output that indicates whether the input voltage is above or below these levels.

The gain booster is integrated to enhance the signal strength, ensuring that the comparators operate effectively even with low-level input signals. This component is essential for maintaining signal integrity and improving the overall dynamic range of the ADC.

The 0-1 generator is responsible for producing a digital signal output based on the comparator's results. This generator translates the analog input into a binary format, which is then processed further by the connected digital circuitry.

Additionally, the ROM (Read-Only Memory) in each row stores calibration data and reference voltages necessary for accurate conversions. This memory component is critical for ensuring that the ADC maintains precision across various operating conditions.

The stacked row configuration allows for a compact design, reducing the overall footprint of the ADC while maximizing the number of channels that can be integrated into a single device. This design choice is particularly beneficial in applications where space is at a premium, such as in mobile devices or high-density circuit boards.

In summary, the TIQ Flash ADC's layout integrates essential components in a row-based architecture, optimizing performance through careful design considerations, including signal boosting, binary conversion, and data storage, all while maintaining a compact form factor suitable for modern electronic applications.The layout design of the TIQ Flash ADC follows closely with the shown circuit diagram. A row layout is designed, and the rows are stacked. A row consists of a comparator, a gain booster, a 0-1 generator, and a ROM (one row). 🔗 External reference

The TIQ Flash ADC architecture utilizes a specific row-based configuration to optimize performance and efficiency. Each row is designed to facilitate the conversion of an analog signal into a digital representation, which is crucial for high-speed applications. The comparator within each row plays a pivotal role by comparing the input voltage against reference levels, generating a binary output that indicates whether the input voltage is above or below these levels.

The gain booster is integrated to enhance the signal strength, ensuring that the comparators operate effectively even with low-level input signals. This component is essential for maintaining signal integrity and improving the overall dynamic range of the ADC.

The 0-1 generator is responsible for producing a digital signal output based on the comparator's results. This generator translates the analog input into a binary format, which is then processed further by the connected digital circuitry.

Additionally, the ROM (Read-Only Memory) in each row stores calibration data and reference voltages necessary for accurate conversions. This memory component is critical for ensuring that the ADC maintains precision across various operating conditions.

The stacked row configuration allows for a compact design, reducing the overall footprint of the ADC while maximizing the number of channels that can be integrated into a single device. This design choice is particularly beneficial in applications where space is at a premium, such as in mobile devices or high-density circuit boards.

In summary, the TIQ Flash ADC's layout integrates essential components in a row-based architecture, optimizing performance through careful design considerations, including signal boosting, binary conversion, and data storage, all while maintaining a compact form factor suitable for modern electronic applications.The layout design of the TIQ Flash ADC follows closely with the shown circuit diagram. A row layout is designed, and the rows are stacked. A row consists of a comparator, a gain booster, a 0-1 generator, and a ROM (one row). 🔗 External reference