Schematics of TTL CPU

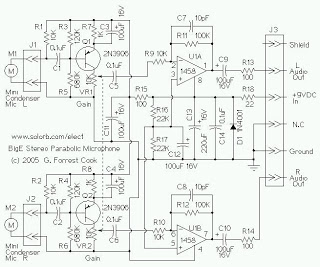

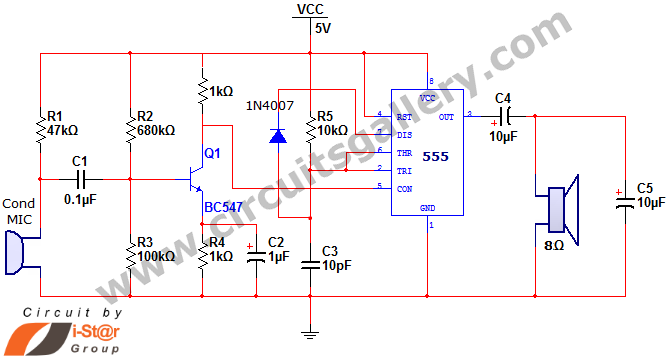

The third Eagle layout of the program counter has been completed, presenting a clearer design compared to the previous iterations, which were cluttered with intersecting wires, making it difficult to discern connections. This diagram is intended to facilitate understanding of the design's objectives. The lines A-0 to A-3 and B-0 to B-3 are integrated into a single 4-bit bus that interfaces with the instruction operand through control circuitry, allowing new addresses to be loaded into the program counter via the JUMP instruction. For testing purposes, pull-up or pull-down resistors or switches should be employed to maintain logic levels. The clock circuit utilizes a simple 555 timer configuration with an adjustable frequency controlled by a potentiometer. While it currently operates, further refinement of component values is necessary to achieve operational speeds exceeding 10Hz. There are concerns regarding the duty cycle balance in relation to frequency, suggesting the need for oscilloscope analysis to investigate the pulse width at higher speeds, as the counters experience stalling beyond 10Hz, which is considered low.

The program counter circuit is designed to facilitate the operation of a digital system by managing the sequence of instruction execution. The integration of A-0 to A-3 and B-0 to B-3 into a single 4-bit bus allows for efficient data transfer between the control unit and the program counter. The control circuitry plays a crucial role in interpreting JUMP instructions, which are essential for altering the flow of execution by loading new addresses into the program counter.

During testing, the implementation of pull-up and pull-down resistors is critical for ensuring stable logic levels on the bus lines. These resistors prevent floating inputs, which could lead to unpredictable behavior in the circuit. The choice of a 555 timer for the clock circuit is advantageous due to its ease of use and versatility; however, achieving higher frequencies necessitates careful selection of component values. The adjustable potentiometer allows for fine-tuning of the clock rate, but the duty cycle must be optimized to ensure reliable operation of the counters.

Oscilloscope measurements will provide valuable insights into the clock signal's characteristics, particularly the pulse width and frequency stability. Observations of stalling behavior in the counters beyond 10Hz indicate that the current design may require adjustments to maintain synchronization at higher speeds. Overall, the layout improvements and the focus on testing methodologies will contribute to the successful implementation of the program counter within the broader digital system.I just finished doing the 3rd Eagle layout of the program counter and this one actually makes sense to look at. The first two were a mess of wires intersecting and crossing over each other so that it was hard to see what was connected and what wasn`t.

Hopefully anyone looking at this diagram can follow along and get what I`m aiming for. A-0 to A-3 and B-0 to B-3 are on the same 4-bit bus that connects to the instruction opperand through the control circuitry so that new addresses can be loaded into the program counter through the JUMP instruction. When testing they should have pull-up/down resistors or switches holding them at hi/low. The clock circuit is a simple 555 circuit with an adjustable rate via a potentiometer. It works for now but I have to refine my component values to make it work at speeds higher than about 10Hz.

I suspect that the duty cycle isn`t well balanced related to the frequency. I`ll have to scope it to see what`s really going on but I think the length of the pulse is too short as the clock speeds up because my counters should be able to work at speed but they start stalling when I get going past 10Hz which is pretty slow. 🔗 External reference

The program counter circuit is designed to facilitate the operation of a digital system by managing the sequence of instruction execution. The integration of A-0 to A-3 and B-0 to B-3 into a single 4-bit bus allows for efficient data transfer between the control unit and the program counter. The control circuitry plays a crucial role in interpreting JUMP instructions, which are essential for altering the flow of execution by loading new addresses into the program counter.

During testing, the implementation of pull-up and pull-down resistors is critical for ensuring stable logic levels on the bus lines. These resistors prevent floating inputs, which could lead to unpredictable behavior in the circuit. The choice of a 555 timer for the clock circuit is advantageous due to its ease of use and versatility; however, achieving higher frequencies necessitates careful selection of component values. The adjustable potentiometer allows for fine-tuning of the clock rate, but the duty cycle must be optimized to ensure reliable operation of the counters.

Oscilloscope measurements will provide valuable insights into the clock signal's characteristics, particularly the pulse width and frequency stability. Observations of stalling behavior in the counters beyond 10Hz indicate that the current design may require adjustments to maintain synchronization at higher speeds. Overall, the layout improvements and the focus on testing methodologies will contribute to the successful implementation of the program counter within the broader digital system.I just finished doing the 3rd Eagle layout of the program counter and this one actually makes sense to look at. The first two were a mess of wires intersecting and crossing over each other so that it was hard to see what was connected and what wasn`t.

Hopefully anyone looking at this diagram can follow along and get what I`m aiming for. A-0 to A-3 and B-0 to B-3 are on the same 4-bit bus that connects to the instruction opperand through the control circuitry so that new addresses can be loaded into the program counter through the JUMP instruction. When testing they should have pull-up/down resistors or switches holding them at hi/low. The clock circuit is a simple 555 circuit with an adjustable rate via a potentiometer. It works for now but I have to refine my component values to make it work at speeds higher than about 10Hz.

I suspect that the duty cycle isn`t well balanced related to the frequency. I`ll have to scope it to see what`s really going on but I think the length of the pulse is too short as the clock speeds up because my counters should be able to work at speed but they start stalling when I get going past 10Hz which is pretty slow. 🔗 External reference