trying to improve on the spi bus

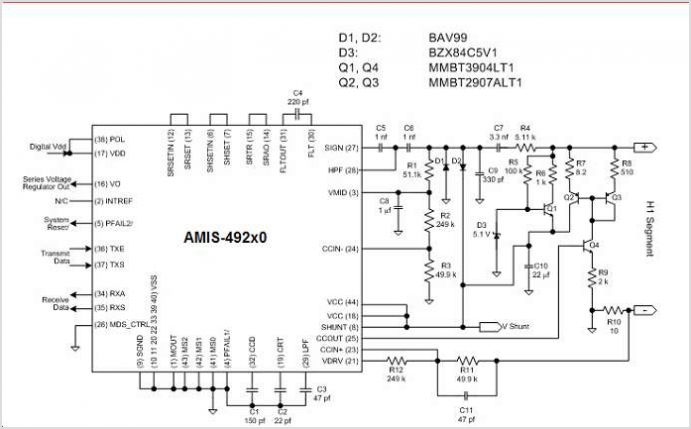

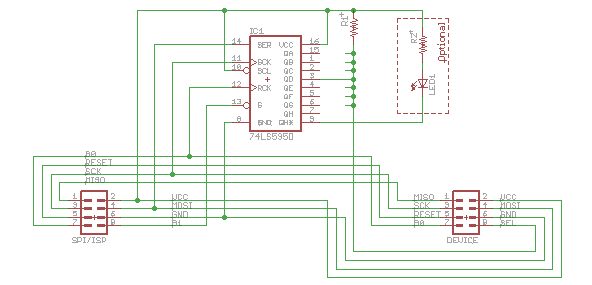

Overcome a major drawback of the SPI bus. The I2C bus is a highly convenient design that requires only four wires to connect multiple chips. Each chip receives the same information but responds only to a specific address located at the beginning of each I2C message. With a single chip, there is no issue: one slave select (SS), a serial clock (SCLK), a master-out slave-in (MOSI) pin for outgoing data, and a master-in slave-out (MISO) pin for incoming data. However, complications arise when multiple chips, or slaves, are involved. While SCLK, MOSI, and MISO pins can be shared, each slave requires a separate slave select pin, which prevents the use of a true bus configuration. To address this limitation, the proposal involves utilizing all SPI signals along with power and two chip select lines, similar to the SPI/ISP connector, using B0 and B1 as the select signals. The approach consists of first sending a byte over SPI with B0 set low, followed by the actual data transfer with B1 set low. The B0 transfer selects a specific slave, while the B1 transfer occurs solely with that slave. A 74HC595 shift register provides the necessary functionality to execute this task, utilizing the three-state enable pin to control the shift register outputs. The schematic involves placing this simple circuit on each slave board, with different outputs from the shift register jumpered for each one. In the schematic, for instance, QD (the fourth bit) is wired as the slave select.

The proposed circuit design effectively addresses the limitations of the SPI bus when connecting multiple slave devices. By implementing a 74HC595 shift register, the circuit can utilize its outputs for slave selection while maintaining the shared SCLK, MOSI, and MISO lines. The shift register's three-state enable pin allows for controlled output activation, enabling seamless communication with individual slaves.

In this configuration, the first transfer over SPI is dedicated to selecting the desired slave device. This is achieved by setting the B0 pin low, which activates the corresponding output on the shift register that is connected to the selected slave's SS pin. Following this, the actual data transfer occurs with B1 set low, ensuring that the data is sent exclusively to the chosen slave. This method simplifies the wiring and reduces the number of required pins on the master device, making it an efficient solution for systems with multiple slave devices.

The schematic for this design should clearly illustrate the connections between the master device, the shift register, and the individual slave devices. Each slave board would have its unique jumper configuration for the shift register outputs, allowing for easy customization and scalability. This design not only optimizes the use of available pins but also enhances the overall functionality of the SPI bus in multi-device applications.Overcome a major drawback of the SPI bus. But to explain this, allow me to go on a little detour first. The I2C bus is an extremely convenient design, because it only needs 4 wires to connect several chips together: Each chip sees the same information, but it works because each chip has been set up to respond only to a specific addre ss on the bus. And that address happens to be conveniently located at the start of each I2C message. With one chip, there`s no problem: one slave select (SS), a serial clock (SCLK), a master-out slave-in (MOSI) pin for outgoing data, and a master-in slave-out (MISO) for incoming data (brilliant naming no confusion!). The trouble is with multiple chips, i. e. slaves. The SCLK, MOSI, and MISO pins can be shared, but not the slave select . Each slave will need a separate pin to select it. And that makes it impossible to use it as a real bus And that`s where yesterday`s post comes in. Suppose we had all the SPI signals, as well as power, as well as two chip selects. Like, eh the SPI/ISP connector, using B0 and B1 as the two select signals how convenient! So here`s the idea: first we send a byte over SPI with B0 set low and then we send the actual data with B1 set low.

The B0 transfer is used to select one specific slave, and the B1 transfer then takes place only with that slave. The good news is that a 74HC595 shift register has all the functionality needed to perform this task, by using the three-state enable pin as a gate to turn the shift register outputs on or off.

Here`s the schematic for it all: The idea is to put this simple circuit on each slave board. On each one, a different output from the shift register gets jumpered. In the above schematic, for example, QD (the 4th bit) has been wired up as slave select. 🔗 External reference

The proposed circuit design effectively addresses the limitations of the SPI bus when connecting multiple slave devices. By implementing a 74HC595 shift register, the circuit can utilize its outputs for slave selection while maintaining the shared SCLK, MOSI, and MISO lines. The shift register's three-state enable pin allows for controlled output activation, enabling seamless communication with individual slaves.

In this configuration, the first transfer over SPI is dedicated to selecting the desired slave device. This is achieved by setting the B0 pin low, which activates the corresponding output on the shift register that is connected to the selected slave's SS pin. Following this, the actual data transfer occurs with B1 set low, ensuring that the data is sent exclusively to the chosen slave. This method simplifies the wiring and reduces the number of required pins on the master device, making it an efficient solution for systems with multiple slave devices.

The schematic for this design should clearly illustrate the connections between the master device, the shift register, and the individual slave devices. Each slave board would have its unique jumper configuration for the shift register outputs, allowing for easy customization and scalability. This design not only optimizes the use of available pins but also enhances the overall functionality of the SPI bus in multi-device applications.Overcome a major drawback of the SPI bus. But to explain this, allow me to go on a little detour first. The I2C bus is an extremely convenient design, because it only needs 4 wires to connect several chips together: Each chip sees the same information, but it works because each chip has been set up to respond only to a specific addre ss on the bus. And that address happens to be conveniently located at the start of each I2C message. With one chip, there`s no problem: one slave select (SS), a serial clock (SCLK), a master-out slave-in (MOSI) pin for outgoing data, and a master-in slave-out (MISO) for incoming data (brilliant naming no confusion!). The trouble is with multiple chips, i. e. slaves. The SCLK, MOSI, and MISO pins can be shared, but not the slave select . Each slave will need a separate pin to select it. And that makes it impossible to use it as a real bus And that`s where yesterday`s post comes in. Suppose we had all the SPI signals, as well as power, as well as two chip selects. Like, eh the SPI/ISP connector, using B0 and B1 as the two select signals how convenient! So here`s the idea: first we send a byte over SPI with B0 set low and then we send the actual data with B1 set low.

The B0 transfer is used to select one specific slave, and the B1 transfer then takes place only with that slave. The good news is that a 74HC595 shift register has all the functionality needed to perform this task, by using the three-state enable pin as a gate to turn the shift register outputs on or off.

Here`s the schematic for it all: The idea is to put this simple circuit on each slave board. On each one, a different output from the shift register gets jumpered. In the above schematic, for example, QD (the 4th bit) has been wired up as slave select. 🔗 External reference