underclock the Super GameBoy

A Super GameBoy was acquired, but it has been observed that the sound pitch is significantly higher than that of an original GameBoy. This discrepancy arises due to a mismatch in CPU clock frequencies: 4.194304 MHz for the original GameBoy and 4.295454 MHz for the Super GameBoy. There is an intention to underclock the Super GameBoy, but the specific connection point for the clock frequency on the CPU is unclear.

To address the issue of mismatched clock frequencies between the Super GameBoy and the original GameBoy, it is essential to understand the clock circuitry within the Super GameBoy. The CPU in the Super GameBoy operates at a frequency of 4.295454 MHz, which is slightly higher than the original GameBoy's 4.194304 MHz. This difference results in a higher sound pitch, which can affect the overall gaming experience.

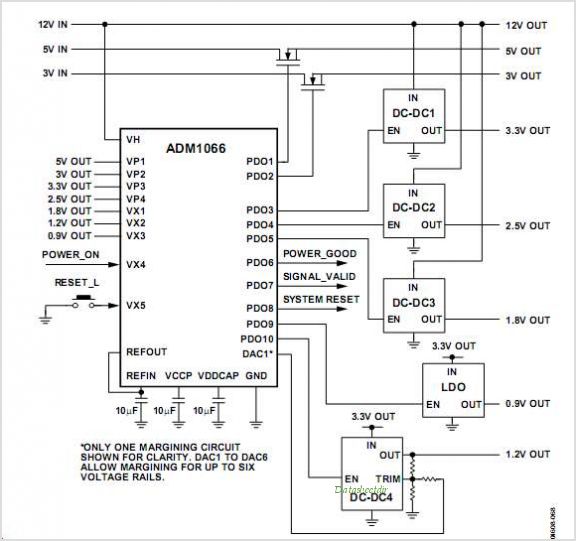

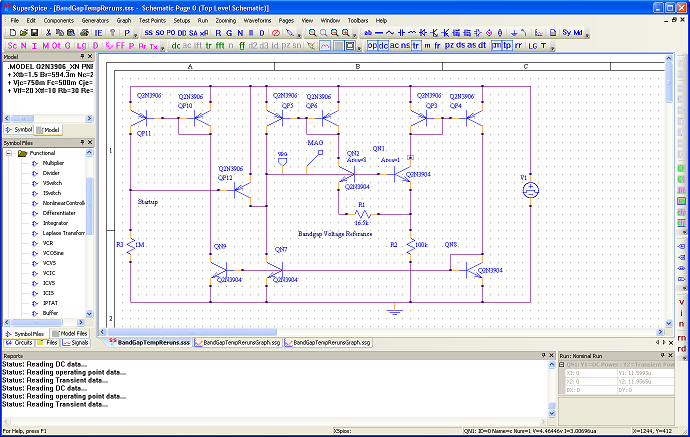

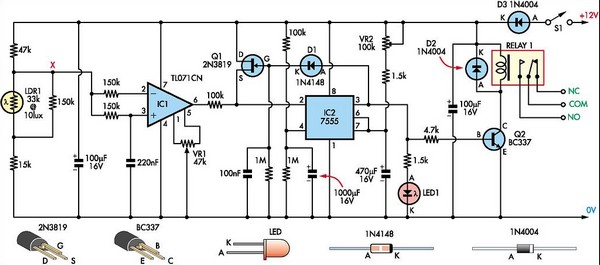

Underclocking the Super GameBoy requires precise modifications to the clock input circuitry. The clock signal for the CPU is typically generated by a crystal oscillator or a phase-locked loop (PLL) circuit. In the case of the Super GameBoy, the clock signal can be found on the main circuit board, usually connected to the CPU's clock input pin.

To successfully underclock the device, one approach involves replacing the existing crystal oscillator with one that has a lower frequency, ideally 4.194304 MHz. Alternatively, if the design allows, a frequency divider circuit could be implemented to reduce the clock frequency without needing to replace the oscillator. This would involve routing the clock signal through a flip-flop or a counter that divides the frequency by a specific factor.

It is critical to ensure that any modifications do not disrupt other functionalities of the Super GameBoy. Therefore, a thorough understanding of the schematic and layout of the circuit board is necessary. Additionally, testing the device after modifications will confirm whether the sound pitch has been successfully adjusted to match that of the original GameBoy.

In summary, addressing the clock frequency mismatch involves identifying the clock signal connections on the CPU and implementing a suitable method for underclocking, either through oscillator replacement or frequency division. This process requires careful consideration of the existing circuitry to maintain the integrity and functionality of the Super GameBoy.I got myself a Super GameBoy today, but I noticed that the sound pitch is notably higher than an original GameBoy(CPU clock frequency doesn`t match between the Super GameBoy and GameBoy "Brick," 4.194304 MHz for the "Brick" and 4.295454 MHz for the Super GameBoy. I`m looking to underclock the thing, but I have no clue where the clock frequency is supposed to be hooked up on the CPU.

The guide I`ve found for the GameBoy "Brick"(this one:.. 🔗 External reference

To address the issue of mismatched clock frequencies between the Super GameBoy and the original GameBoy, it is essential to understand the clock circuitry within the Super GameBoy. The CPU in the Super GameBoy operates at a frequency of 4.295454 MHz, which is slightly higher than the original GameBoy's 4.194304 MHz. This difference results in a higher sound pitch, which can affect the overall gaming experience.

Underclocking the Super GameBoy requires precise modifications to the clock input circuitry. The clock signal for the CPU is typically generated by a crystal oscillator or a phase-locked loop (PLL) circuit. In the case of the Super GameBoy, the clock signal can be found on the main circuit board, usually connected to the CPU's clock input pin.

To successfully underclock the device, one approach involves replacing the existing crystal oscillator with one that has a lower frequency, ideally 4.194304 MHz. Alternatively, if the design allows, a frequency divider circuit could be implemented to reduce the clock frequency without needing to replace the oscillator. This would involve routing the clock signal through a flip-flop or a counter that divides the frequency by a specific factor.

It is critical to ensure that any modifications do not disrupt other functionalities of the Super GameBoy. Therefore, a thorough understanding of the schematic and layout of the circuit board is necessary. Additionally, testing the device after modifications will confirm whether the sound pitch has been successfully adjusted to match that of the original GameBoy.

In summary, addressing the clock frequency mismatch involves identifying the clock signal connections on the CPU and implementing a suitable method for underclocking, either through oscillator replacement or frequency division. This process requires careful consideration of the existing circuitry to maintain the integrity and functionality of the Super GameBoy.I got myself a Super GameBoy today, but I noticed that the sound pitch is notably higher than an original GameBoy(CPU clock frequency doesn`t match between the Super GameBoy and GameBoy "Brick," 4.194304 MHz for the "Brick" and 4.295454 MHz for the Super GameBoy. I`m looking to underclock the thing, but I have no clue where the clock frequency is supposed to be hooked up on the CPU.

The guide I`ve found for the GameBoy "Brick"(this one:.. 🔗 External reference