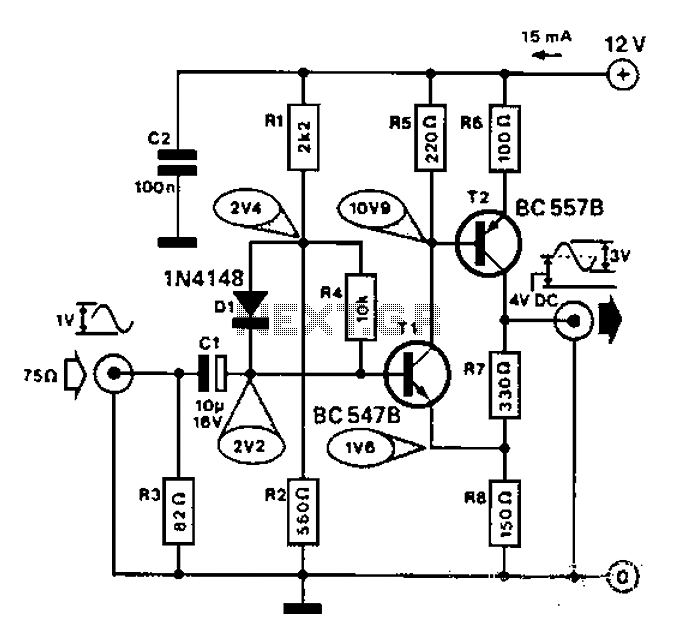

Video Selector Circuit

This circuit selects one of two channels using a logic signal. The unused channel is shorted out to minimize crosstalk. The bandwidth at -3 dB is approximately 8 MHz. It is recommended to buffer this circuit due to some loss in the switches when driving a 75-Ohm load.

The circuit operates as a channel selector, utilizing electronic switches to determine which of the two input channels is connected to the output. The logic signal controls the state of the switches, allowing for seamless transition between channels. When one channel is active, the other is shorted to ground, effectively eliminating any potential interference or crosstalk that could affect the quality of the signal.

The design ensures that the bandwidth of the circuit remains stable, with a -3 dB point at around 8 MHz, making it suitable for various applications that require signal integrity within this frequency range. The choice of components, including the switches and any associated passive elements, should be carefully considered to maintain performance specifications.

Buffering the circuit is crucial, particularly when interfacing with a 75-Ohm load. The switches may introduce insertion loss, which could degrade the signal if not adequately addressed. By incorporating a buffer stage, the circuit can provide the necessary drive strength and impedance matching, ensuring that the output signal remains robust and undistorted. This additional buffering stage can be implemented using an operational amplifier configured as a voltage follower or a dedicated buffer IC designed for high-frequency applications.

Overall, this circuit is effective for channel selection in communication systems, where maintaining signal quality and minimizing crosstalk are critical for optimal performance. This circuit selects one of two channels with a logic signal. The unused channel is shorted out, which minimizes crosstalk. The bandwidth at -3 dB is about 8 MHz. It is advisable to buffer this circuit because there is some loss in the switches when feeding a 75-Ohm load.

The circuit operates as a channel selector, utilizing electronic switches to determine which of the two input channels is connected to the output. The logic signal controls the state of the switches, allowing for seamless transition between channels. When one channel is active, the other is shorted to ground, effectively eliminating any potential interference or crosstalk that could affect the quality of the signal.

The design ensures that the bandwidth of the circuit remains stable, with a -3 dB point at around 8 MHz, making it suitable for various applications that require signal integrity within this frequency range. The choice of components, including the switches and any associated passive elements, should be carefully considered to maintain performance specifications.

Buffering the circuit is crucial, particularly when interfacing with a 75-Ohm load. The switches may introduce insertion loss, which could degrade the signal if not adequately addressed. By incorporating a buffer stage, the circuit can provide the necessary drive strength and impedance matching, ensuring that the output signal remains robust and undistorted. This additional buffering stage can be implemented using an operational amplifier configured as a voltage follower or a dedicated buffer IC designed for high-frequency applications.

Overall, this circuit is effective for channel selection in communication systems, where maintaining signal quality and minimizing crosstalk are critical for optimal performance. This circuit selects one of two channels with a logic signal. The unused channel is shorted out, which minimizes crosstalk. The bandwidth at -3 dB is about 8 MHz. It is advisable to buffer this circuit because there is some loss in the switches when feeding a 75-Ohm load.