555 DC Voltage Doubler Circuit

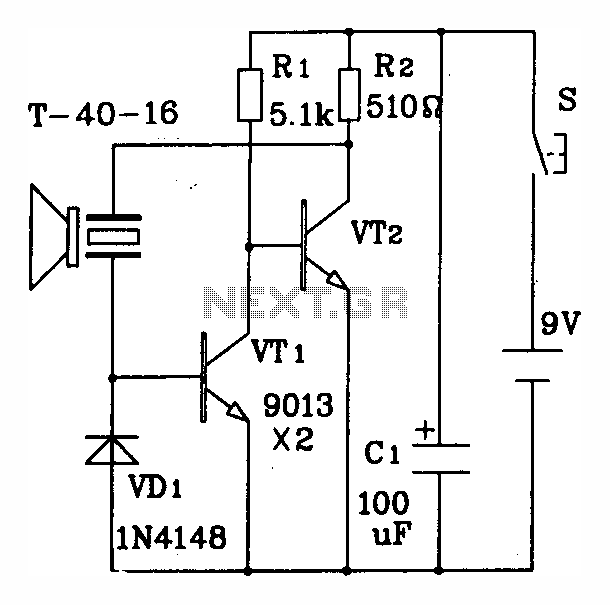

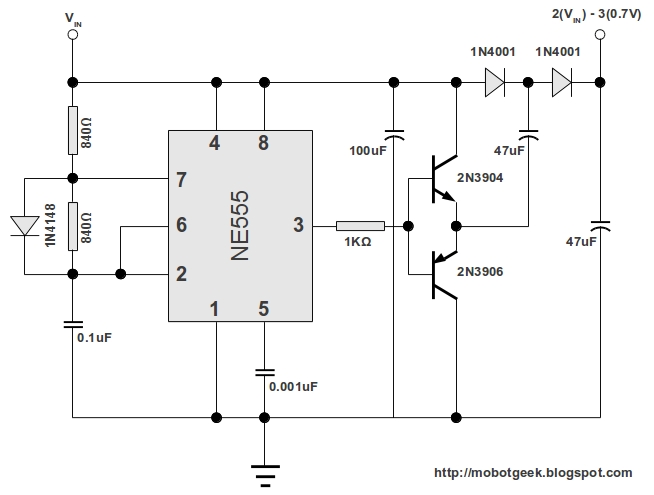

This DC voltage doubler circuit generates a voltage that is double its supply voltage. It is advantageous when a higher voltage level is required from a single lower voltage power supply. Due to the low current consumption in such applications, the circuit can be constructed with minimal components. The circuit primarily consists of a square wave generator utilizing the common LM555 timer IC, followed by a final stage comprising transistors T1 and T2. The voltage doubler circuit includes components D1, D2, C4, and C5. The LM555 timer operates as an astable multivibrator, producing a frequency of approximately 8.5 kHz. The square wave output drives the final stage made up of T1 and T2. The operation of the doubler is as follows: during a low amplitude signal, transistor T1 remains off while T2 conducts. The negative terminal of capacitor C4 is grounded, allowing it to charge through D1. Conversely, during a high amplitude signal, T1 conducts while T2 turns off. Capacitor C4 cannot discharge due to D1's blocking action. Consequently, capacitor C5 is charged with a combined voltage from C4 and the power supply (12V input). In standby mode, the circuit outputs approximately 20 volts, with a maximum load not exceeding 70 mA. The actual output voltage is around 18 volts, yielding an efficiency rating of 32%. For applications requiring a stable voltage level, a three-pin voltage regulator IC can be added to the output. The current consumption of the regulator IC must be accounted for in the total current consumption, which should not exceed 70 mA.

This DC voltage doubler circuit is designed to efficiently convert a lower input voltage into a higher output voltage, making it suitable for various electronic applications where increased voltage is necessary without the need for a separate power supply. The use of the LM555 timer IC as an astable multivibrator is instrumental in generating the required square wave signal, which is essential for the operation of the subsequent transistor stage.

The transistors T1 and T2 play a crucial role in the voltage doubling process by alternating their conductive states in response to the square wave signal. This switching action allows for the charging of capacitors C4 and C5, effectively stacking the voltages. The diodes D1 and D2 ensure that the current flows in the correct direction, preventing backflow and maintaining the charge in the capacitors.

The circuit's design emphasizes simplicity and efficiency, utilizing readily available components. The output voltage can reach up to 20 volts under no-load conditions, while the actual output voltage settles around 18 volts under load, demonstrating the effectiveness of the voltage doubling process. The specified maximum load of 70 mA ensures that the circuit operates within safe limits, maintaining reliability and longevity.

In applications where voltage stability is critical, integrating a voltage regulator IC at the output can enhance performance by providing a consistent output voltage despite variations in load or input voltage. However, it is essential to consider the additional current draw from the regulator to avoid exceeding the circuit's maximum current capacity. This careful consideration ensures optimal performance and reliability in practical applications.This dc voltage doubler circuit produces a voltage that is twice its voltage supply. This is useful when a higher voltage level is needed out of a single lower voltage power supply. Since the current consumption levels are low in such cases, the circuit can be built with minimal resources. The electronic circuit is basically a square wave generato r using the common LM555 timer IC. It is followed by a final stage made of transistors T1 and T2. The actual doubler circuit is made of D1, D2, C4 and C5 components. The 555 dc voltage doubler timer IC works as an astable multivibrator and generates a frequency of about 8. 5 kHz. The quare wave output drives the final stage made of T1 and T2. This is how the doubler works: by a low amplitude of the signal, transistor T1 blocks while T2 conducts.

The minus electrode of the capacitor C4 is grounded and charges through D1. By a high amplitude of the signal, transistor T1 conducts while T2 blocks. However, capacitor C4 cannot discharge because it is blocked by D1. The following capacitor C5 is therefore charged with a combined voltage from C4 and the power supply (12V input). On standby, the circuit delivers around 20 volts. The maximum load must not exceed 70 mA. The actual output voltage is around 18 volts giving an efficiency rating of 32 %. If a stable voltage lever is desired, a 3 pin voltage regulator IC can be added at the output. The regulator IC`s own current consumption must be added to the total current consumption which must not exceed 70 mA.

🔗 External reference

This DC voltage doubler circuit is designed to efficiently convert a lower input voltage into a higher output voltage, making it suitable for various electronic applications where increased voltage is necessary without the need for a separate power supply. The use of the LM555 timer IC as an astable multivibrator is instrumental in generating the required square wave signal, which is essential for the operation of the subsequent transistor stage.

The transistors T1 and T2 play a crucial role in the voltage doubling process by alternating their conductive states in response to the square wave signal. This switching action allows for the charging of capacitors C4 and C5, effectively stacking the voltages. The diodes D1 and D2 ensure that the current flows in the correct direction, preventing backflow and maintaining the charge in the capacitors.

The circuit's design emphasizes simplicity and efficiency, utilizing readily available components. The output voltage can reach up to 20 volts under no-load conditions, while the actual output voltage settles around 18 volts under load, demonstrating the effectiveness of the voltage doubling process. The specified maximum load of 70 mA ensures that the circuit operates within safe limits, maintaining reliability and longevity.

In applications where voltage stability is critical, integrating a voltage regulator IC at the output can enhance performance by providing a consistent output voltage despite variations in load or input voltage. However, it is essential to consider the additional current draw from the regulator to avoid exceeding the circuit's maximum current capacity. This careful consideration ensures optimal performance and reliability in practical applications.This dc voltage doubler circuit produces a voltage that is twice its voltage supply. This is useful when a higher voltage level is needed out of a single lower voltage power supply. Since the current consumption levels are low in such cases, the circuit can be built with minimal resources. The electronic circuit is basically a square wave generato r using the common LM555 timer IC. It is followed by a final stage made of transistors T1 and T2. The actual doubler circuit is made of D1, D2, C4 and C5 components. The 555 dc voltage doubler timer IC works as an astable multivibrator and generates a frequency of about 8. 5 kHz. The quare wave output drives the final stage made of T1 and T2. This is how the doubler works: by a low amplitude of the signal, transistor T1 blocks while T2 conducts.

The minus electrode of the capacitor C4 is grounded and charges through D1. By a high amplitude of the signal, transistor T1 conducts while T2 blocks. However, capacitor C4 cannot discharge because it is blocked by D1. The following capacitor C5 is therefore charged with a combined voltage from C4 and the power supply (12V input). On standby, the circuit delivers around 20 volts. The maximum load must not exceed 70 mA. The actual output voltage is around 18 volts giving an efficiency rating of 32 %. If a stable voltage lever is desired, a 3 pin voltage regulator IC can be added at the output. The regulator IC`s own current consumption must be added to the total current consumption which must not exceed 70 mA.

🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713