Analog De-Glitch Circuit Circuit

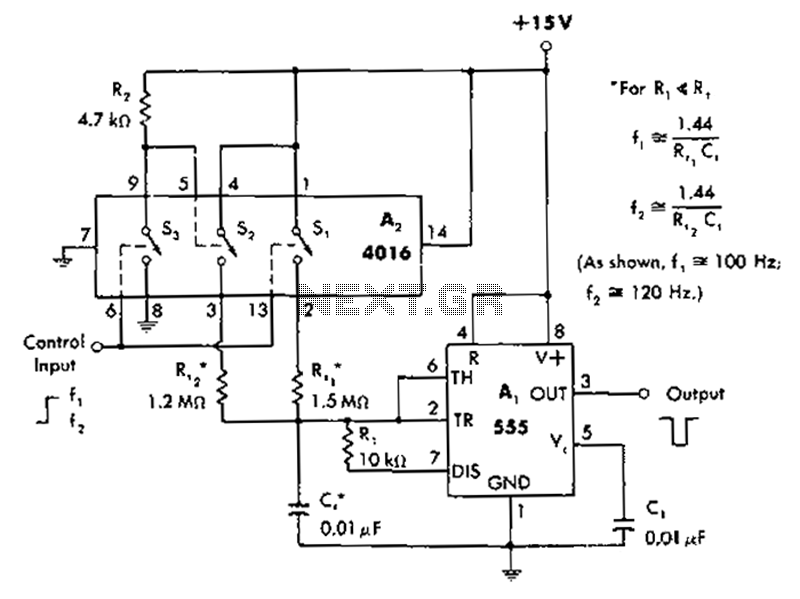

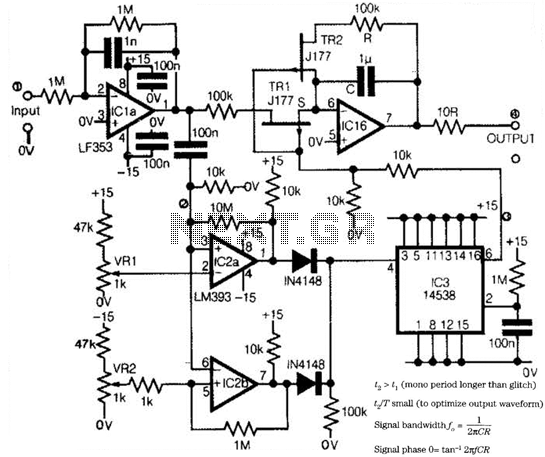

Low-frequency signals produced by transducers, measurement equipment, or data loggers often resemble the first waveform in the figure. The circuit operates as a tracking sample-and-hold, where transients are replaced in the output by the stored value of the current signal at the moment of the transient. The input signal is buffered and inverted by IC1a, and the differentiated result is applied to the inputs of two comparators, IC2-a and IC2-b. VR1 and VR2 set levels to avoid false or unnecessary operation. Either comparator output triggers the monostable multivibrator IC3 in response to positive or negative signal transients. When IC3 is not triggered, transistors TR1 and TR2, which are p-channel JFETs, are on, allowing IC1b to function as an integrator with high leakage, tracking the input signal. Upon triggering of the monostable, as shown at point 3, TR1 and TR2 turn off, and the previous signal value is held constant, as depicted at point 4. The resulting output waveform can be filtered to remove harmonics from the restoring step at the end of the monostable period, if necessary. The signal range is approximately 5 V, depending on the amplitude and polarity of the transient. The monostable period illustrated is 100 ms, but this can be optimized for practical applications. A shorter monostable period relative to the signal waveform improves the quality of the output.

This circuit functions effectively for capturing and holding low-frequency signals, making it suitable for various applications in measurement and data logging. The use of a tracking sample-and-hold configuration allows for accurate representation of transient signals, which is crucial in scenarios where signal integrity is paramount. The buffering and inversion of the input signal by IC1a ensures that the subsequent processing stages receive a stable and appropriately conditioned signal.

The differentiation stage provides the necessary signal transitions that are critical for the operation of the comparators. The adjustable reference levels set by VR1 and VR2 are essential for preventing false triggering, which could lead to erroneous outputs. The design incorporates two comparators to enhance reliability, as either can trigger the monostable multivibrator IC3, thereby providing a fail-safe mechanism.

The integration function performed by IC1b during the inactive state of IC3 allows for continuous tracking of the input signal, ensuring that the circuit can respond dynamically to signal changes. The transition to a hold state upon triggering of the monostable is a key feature, allowing for the output to maintain a stable value that can be processed further.

The output waveform's ability to be filtered enhances its utility, allowing for the removal of unwanted harmonics that may arise from the switching action of the monostable. This capability is particularly useful in applications where signal fidelity is critical, such as in audio processing or precision measurement systems.

The consideration of the monostable period is also significant; optimizing this duration relative to the input signal characteristics can lead to improved performance. A shorter monostable period relative to the signal waveform allows for more accurate representation of the signal's dynamics, which is beneficial in high-speed applications.

Overall, this circuit design exemplifies a robust approach to low-frequency signal processing, balancing the need for accurate signal tracking with the ability to hold and filter signals effectively. Low-frequency signals produced by transducers, measurement equipment, or data loggers often appear like the first waveform in the figure. The circuit shown operates as a tracking sample-hold, and the transients are replaced in the output by the stored value of the current signal at the instant of the transient.

The input signal is buffered and inverted by ICla, and the differentiated result shown at 2 applied to the inputs of two comparators IC2-a and IC2-b. VR1 and VR2 set levels to prevent false or unnecessary operation. Either comparator output triggers the mono IC3 from positive or negative signal transients. When IC3 has not been triggered, TR1 and TR2 *p` channel JFETs are on, and IClb operates as an integrator with a high leakage, and tracks the input signal. When the mono is triggered as at 3, TR1 and TR2 turn off and the previous signal value is held constant, as shown at 4.

The resulting output waveform can then be easily filtered to remove the harmonics from the restoring step at the end of the mono period, if needed. The signal range is approximately 5 V, depending on the transient amplitude and polarity. The mono period shown is 100 mS, but this can be optimized in practical applications. The shorter the mono period in relation to the signal waveform, the better the quality of the result.

This circuit functions effectively for capturing and holding low-frequency signals, making it suitable for various applications in measurement and data logging. The use of a tracking sample-and-hold configuration allows for accurate representation of transient signals, which is crucial in scenarios where signal integrity is paramount. The buffering and inversion of the input signal by IC1a ensures that the subsequent processing stages receive a stable and appropriately conditioned signal.

The differentiation stage provides the necessary signal transitions that are critical for the operation of the comparators. The adjustable reference levels set by VR1 and VR2 are essential for preventing false triggering, which could lead to erroneous outputs. The design incorporates two comparators to enhance reliability, as either can trigger the monostable multivibrator IC3, thereby providing a fail-safe mechanism.

The integration function performed by IC1b during the inactive state of IC3 allows for continuous tracking of the input signal, ensuring that the circuit can respond dynamically to signal changes. The transition to a hold state upon triggering of the monostable is a key feature, allowing for the output to maintain a stable value that can be processed further.

The output waveform's ability to be filtered enhances its utility, allowing for the removal of unwanted harmonics that may arise from the switching action of the monostable. This capability is particularly useful in applications where signal fidelity is critical, such as in audio processing or precision measurement systems.

The consideration of the monostable period is also significant; optimizing this duration relative to the input signal characteristics can lead to improved performance. A shorter monostable period relative to the signal waveform allows for more accurate representation of the signal's dynamics, which is beneficial in high-speed applications.

Overall, this circuit design exemplifies a robust approach to low-frequency signal processing, balancing the need for accurate signal tracking with the ability to hold and filter signals effectively. Low-frequency signals produced by transducers, measurement equipment, or data loggers often appear like the first waveform in the figure. The circuit shown operates as a tracking sample-hold, and the transients are replaced in the output by the stored value of the current signal at the instant of the transient.

The input signal is buffered and inverted by ICla, and the differentiated result shown at 2 applied to the inputs of two comparators IC2-a and IC2-b. VR1 and VR2 set levels to prevent false or unnecessary operation. Either comparator output triggers the mono IC3 from positive or negative signal transients. When IC3 has not been triggered, TR1 and TR2 *p` channel JFETs are on, and IClb operates as an integrator with a high leakage, and tracks the input signal. When the mono is triggered as at 3, TR1 and TR2 turn off and the previous signal value is held constant, as shown at 4.

The resulting output waveform can then be easily filtered to remove the harmonics from the restoring step at the end of the mono period, if needed. The signal range is approximately 5 V, depending on the transient amplitude and polarity. The mono period shown is 100 mS, but this can be optimized in practical applications. The shorter the mono period in relation to the signal waveform, the better the quality of the result.