Compensation Resistor Stabilizes SMPS at High Duty Cycles

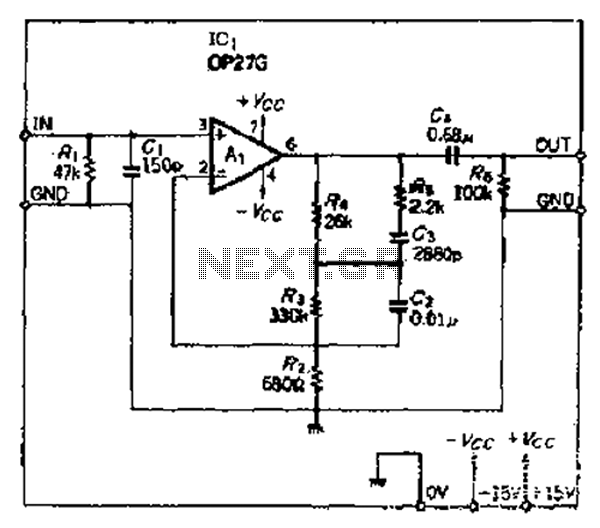

Current-controlled switching-mode power supplies (SMPS) are increasingly popular due to their ability to allow pulse-by-pulse current control and monitoring, enhancing reliability and robustness compared to voltage-controlled alternatives. Current control also removes a positive zero in certain transfer functions, contributing to greater stability. However, at pulse duty cycles exceeding 0.5, current-controlled SMPS can become unstable, oscillating at half of the switching frequency. To stabilize the circuit, designers must adjust the slope of the pulses sent to the pulse-width modulation (PWM) comparator. This adjustment can be achieved by adding a sawtooth voltage derived from the voltage across the timing capacitor to the voltage developed across the current-sensing resistor. Alternatively, a sufficient current slope can be introduced via a slope-shaping resistor before summing the voltage across the slope-shaping resistor and the current-sensing resistor in the output circuit of the current-sensing transformer. This concept outlines the computation of the slope compensation resistor, Rsl, necessary for achieving the desired voltage pulse slope. The analysis references a simplified schematic of a bridge converter, part of a current-control SMPS, which illustrates how designers can calculate the slope-compensation resistor value to ensure stable operation. The voltage pulse slope is directed to the current-sensing input of U1, an LTC3722-1 synchronous dual-mode phase-modulated full-bridge controller, featuring an internal current-ramping source with a peak current of 74 µA. This internal current generates the compensation slope, which combines with the slope of the pulse across the current-sensing resistor, Rcs, ensuring stability in the current feedback loop at any duty cycle. The computation begins with known factors such as the SMPS output power, voltage, switching frequency, and other parameters determined during power supply analysis. Assuming the pulses across the secondary winding of transformer TR have an amplitude of Vsec, and neglecting the voltage drop across rectifier D2, the duty cycle of the rectified pulses is represented as D. It is important to note that Vload is not the RMS value of Vsec. The current ripple in the filter inductor, ΔiL, can be derived from these parameters. If the current transformer, TC, has one turn on the primary side and wct turns on the secondary, the current-sensing resistor current is represented as Δics. In some cases, the IC's current-sensing input may have a current-limiting threshold, Vth. If necessary to prevent reaching the current-limiting mode, Rcs can be calculated accordingly. If the controller IC does not provide the required current sawtooth waveform, it can be generated from the voltage across the timing capacitor by adding a simple power amplifier based on two complementary bipolar transistors.

The implementation of current-controlled SMPS involves several critical design considerations. The stability of the power supply is paramount, especially when operating at high duty cycles. The introduction of slope compensation is essential to mitigate the risk of instability due to oscillations in the control loop. The slope compensation resistor, Rsl, is calculated based on the specific operational parameters of the SMPS, including the switching frequency and output characteristics.

In practical applications, the design may involve integrating the LTC3722-1 controller, which provides robust features for current-mode control. The internal current ramping source plays a vital role in generating the necessary slope for stable operation. The designer must ensure that the voltage pulse slope is adequately shaped to maintain stability across varying load conditions and duty cycles.

The analysis of the current ripple in the filter inductor, ΔiL, is crucial for determining the appropriate inductor size and type, which directly impacts the overall efficiency and performance of the SMPS. The choice of current-sensing resistor, Rcs, must also consider the current-limiting threshold, Vth, to prevent the system from entering a limiting mode under fault conditions.

In summary, current-controlled SMPS systems offer significant advantages in terms of stability and reliability, particularly when implemented with careful attention to slope compensation and current sensing. The design process requires a thorough understanding of the operational parameters and the interaction between various components within the circuit.Current-control switching-mode power supplies (SMPS) are gaining in popularity because they allow pulse-by-pulse current control and monitoring, making them more reliable and robust than their voltage-controlled counterparts. Current control also eliminates a positive zero in some transfer functions, which makes the supplies more stable.

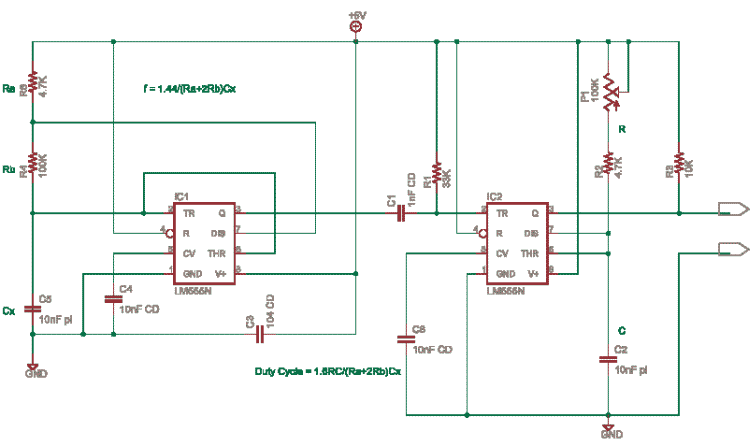

However, at pulse duty cycles above 0. 5, current-control SMPS become unstable, oscillating at half of the switching frequency. 1 To stabilize the circuit, the designer must change the slope of the pulses going to the pulse-width modulation (PWM) comparator. 2 This can be done by adding a sawtooth voltage derived from the voltage across the timing capacitor to the voltage developed across the current-sensing resistor.

Or, you can add a high-enough current slope to the slope-shaping resistor before summing the voltage across the slope-shaping resistor and the current-sensing resistor in the current-sensing transformer`s output circuit. This idea describes how to compute the value of the slope compensation resistor, Rsl, that will create the desired voltage pulse slope.

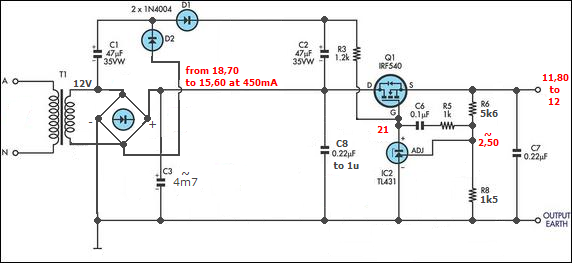

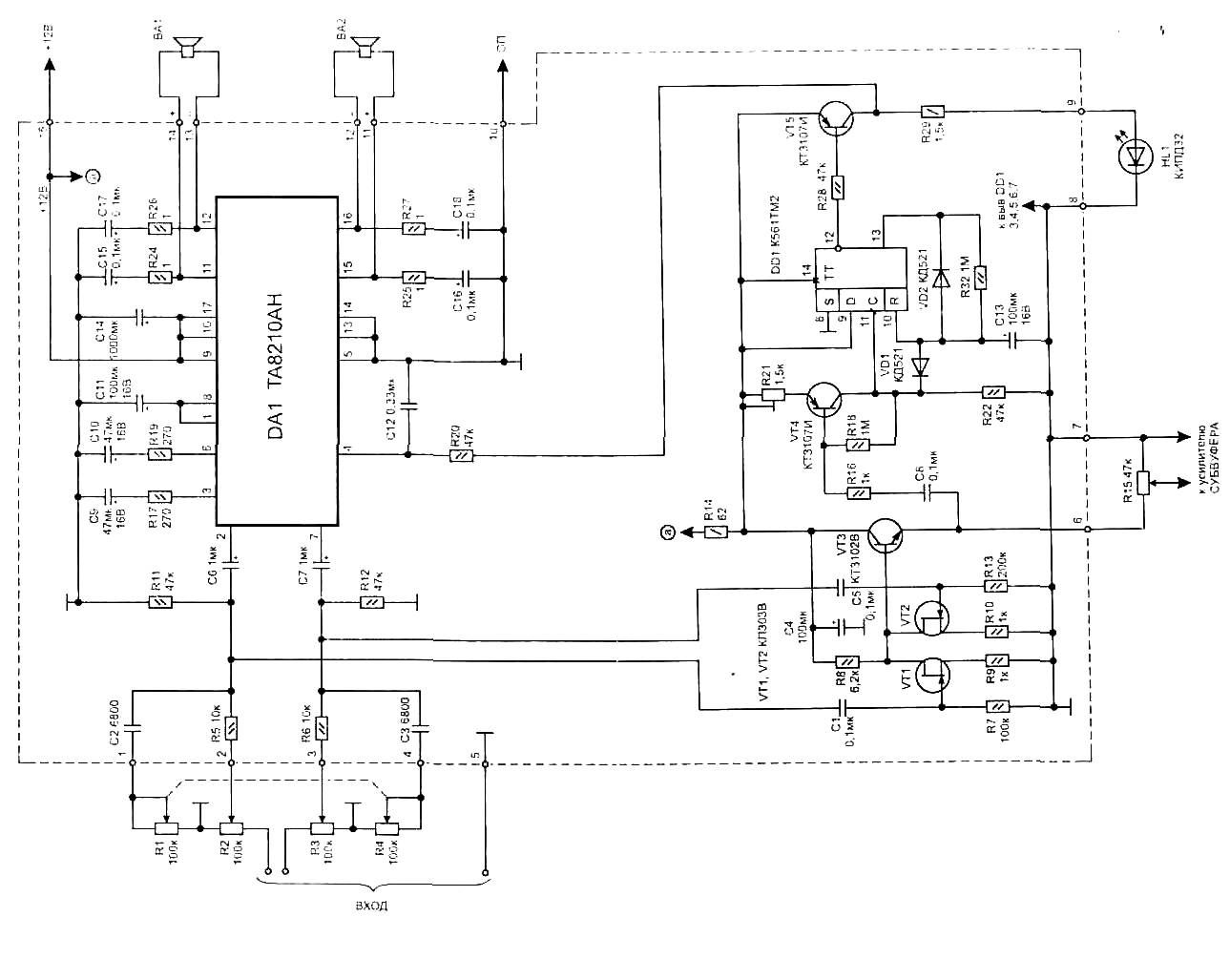

The analysis uses Figure 1, which is part of a bridge converter that is a component of a current-control SMPS. Although the figure is a simplified schematic that denotes rectifiers as diodes and does not show the full bridge, it is suitable for this analysis.

1. This simplified schematic of part of a bridge converter that is a component of a current-control SMPS illustrates how designers can compute the value of a slope-compensation resistor to ensure stable operation. The voltage pulse slope is sent to the current-sensing input of U1, an LTC3722-1 synchronous dual-mode phase-modulated full-bridge controller with an internal current-ramping source whose peak current reaches 74 µA.

This internally generated current creates the compensation slope that adds to the slope of a pulse that is developed across the current sensing resistor, Rcs, making the current feedback loop stable at any duty cycle. The computation starts with the known factors: the SMPS output power, voltage, switching frequency, and other parameters that are obtained during the power supply analysis.

Assuming that the pulses across the secondary winding of transformer TR have an amplitude of Vsec, and neglecting the voltage drop across rectifier D2, which may be a synchronous low-dropout type: where D is the duty cycle of the rectified pulses. Note that Vload is not the rms value of Vsec. Then, the current ripple in the filter inductor, †iL, is: Assuming that the current transformer, TC, has one turn on the primary side and wct turns on the secondary, and the current-sensing resistor current is †ics: Sometimes, however, the IC`s current-sensing input has a current-limiting threshold, Vth.

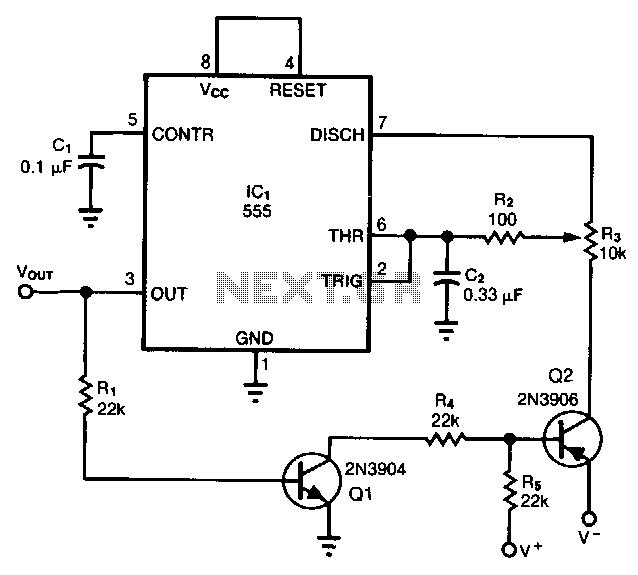

If needed to avoid reaching the current-limiting mode, Rcs may be calculated using: If the controller IC that you employ does not provide the required current sawtoooth waveform, you can derive it from the voltage across the timing capacitor. Just add a simple power amplifier based on two complementary bipolar transistors. Good article Greg. Nicely done. But I don`t think you have spent much time working with current mode control on the bench. If you did, you`d have seen and then later derived in disbelief that the fast inside current loop in avg current mode or peak cmc removes one of the poles in the double pole filter formed by the output inductor and capacitor.

Further, it gives you a built in `feedforward` in that it corrects for input perturbations as fast as the pwm comparator can see the deviatiation in the V/L of the output filter inductor. Not actually a feedforward, but WAY quicker than the voltage loop. As for stability, yes, the academics will all agree that slope compensation is NEEDED to reset the ramp signal to the PWM at duty cycles above 50%.

it`s easy enough to draw that out on paper considering di/d 🔗 External reference

The implementation of current-controlled SMPS involves several critical design considerations. The stability of the power supply is paramount, especially when operating at high duty cycles. The introduction of slope compensation is essential to mitigate the risk of instability due to oscillations in the control loop. The slope compensation resistor, Rsl, is calculated based on the specific operational parameters of the SMPS, including the switching frequency and output characteristics.

In practical applications, the design may involve integrating the LTC3722-1 controller, which provides robust features for current-mode control. The internal current ramping source plays a vital role in generating the necessary slope for stable operation. The designer must ensure that the voltage pulse slope is adequately shaped to maintain stability across varying load conditions and duty cycles.

The analysis of the current ripple in the filter inductor, ΔiL, is crucial for determining the appropriate inductor size and type, which directly impacts the overall efficiency and performance of the SMPS. The choice of current-sensing resistor, Rcs, must also consider the current-limiting threshold, Vth, to prevent the system from entering a limiting mode under fault conditions.

In summary, current-controlled SMPS systems offer significant advantages in terms of stability and reliability, particularly when implemented with careful attention to slope compensation and current sensing. The design process requires a thorough understanding of the operational parameters and the interaction between various components within the circuit.Current-control switching-mode power supplies (SMPS) are gaining in popularity because they allow pulse-by-pulse current control and monitoring, making them more reliable and robust than their voltage-controlled counterparts. Current control also eliminates a positive zero in some transfer functions, which makes the supplies more stable.

However, at pulse duty cycles above 0. 5, current-control SMPS become unstable, oscillating at half of the switching frequency. 1 To stabilize the circuit, the designer must change the slope of the pulses going to the pulse-width modulation (PWM) comparator. 2 This can be done by adding a sawtooth voltage derived from the voltage across the timing capacitor to the voltage developed across the current-sensing resistor.

Or, you can add a high-enough current slope to the slope-shaping resistor before summing the voltage across the slope-shaping resistor and the current-sensing resistor in the current-sensing transformer`s output circuit. This idea describes how to compute the value of the slope compensation resistor, Rsl, that will create the desired voltage pulse slope.

The analysis uses Figure 1, which is part of a bridge converter that is a component of a current-control SMPS. Although the figure is a simplified schematic that denotes rectifiers as diodes and does not show the full bridge, it is suitable for this analysis.

1. This simplified schematic of part of a bridge converter that is a component of a current-control SMPS illustrates how designers can compute the value of a slope-compensation resistor to ensure stable operation. The voltage pulse slope is sent to the current-sensing input of U1, an LTC3722-1 synchronous dual-mode phase-modulated full-bridge controller with an internal current-ramping source whose peak current reaches 74 µA.

This internally generated current creates the compensation slope that adds to the slope of a pulse that is developed across the current sensing resistor, Rcs, making the current feedback loop stable at any duty cycle. The computation starts with the known factors: the SMPS output power, voltage, switching frequency, and other parameters that are obtained during the power supply analysis.

Assuming that the pulses across the secondary winding of transformer TR have an amplitude of Vsec, and neglecting the voltage drop across rectifier D2, which may be a synchronous low-dropout type: where D is the duty cycle of the rectified pulses. Note that Vload is not the rms value of Vsec. Then, the current ripple in the filter inductor, †iL, is: Assuming that the current transformer, TC, has one turn on the primary side and wct turns on the secondary, and the current-sensing resistor current is †ics: Sometimes, however, the IC`s current-sensing input has a current-limiting threshold, Vth.

If needed to avoid reaching the current-limiting mode, Rcs may be calculated using: If the controller IC that you employ does not provide the required current sawtoooth waveform, you can derive it from the voltage across the timing capacitor. Just add a simple power amplifier based on two complementary bipolar transistors. Good article Greg. Nicely done. But I don`t think you have spent much time working with current mode control on the bench. If you did, you`d have seen and then later derived in disbelief that the fast inside current loop in avg current mode or peak cmc removes one of the poles in the double pole filter formed by the output inductor and capacitor.

Further, it gives you a built in `feedforward` in that it corrects for input perturbations as fast as the pwm comparator can see the deviatiation in the V/L of the output filter inductor. Not actually a feedforward, but WAY quicker than the voltage loop. As for stability, yes, the academics will all agree that slope compensation is NEEDED to reset the ramp signal to the PWM at duty cycles above 50%.

it`s easy enough to draw that out on paper considering di/d 🔗 External reference