Custom Silicon Solutions

Doug Grant's article on Heathkit in his blog via the EDN Network reflects on his experience building his first Heathkit and the knowledge he gained. He suggests that every electrical engineer has built at least one kit, a notion he believes to be true. However, he notes that Heathkit eventually declined. The author has constructed several kits, including an oscilloscope, a solid-state FM tuner and amplifier, and a color TV, all of which functioned well and were extensively utilized. The primary benefit was the hands-on learning experience and knowledge acquired during the kit assembly process. The building instructions were consistently clear, and the circuit operation explanations provided a foundational understanding of electronics. Learning to solder was particularly valuable. Doug's blog features a link to an individual contemplating reintroducing the kits and includes his suggestion for a new kit. Numerous comments on the blog share personal experiences with Heathkit and related recommendations. The author believes that Heathkit offered excellent products during its operational period and appreciates the opportunity to learn through their kits. Custom Silicon Solutions (CSS) has partnered with Sarnoff/SRI to design a CMOS image sensor intended for the Naval Research Laboratory's Solar Orbiter Heliospheric Imager (SoloHI). This initiative continues a long-standing collaboration with Sarnoff, having completed 16 previous tape-outs of new designs. This will mark the first instance of a large-format APS detector being deployed in space. The instrument aims to capture high-resolution images of the solar corona and solar wind, including coronal mass ejections (CMEs), to study their propagation and interaction with the solar wind. With a broad field of view, SoloHI will connect remote sensing observations of the corona to in-situ plasma measurements at the spacecraft. A review of an application of the CSS555 Timer IC by Steve Schuler on his blog, Square_Root_of_Not, illustrates how to utilize the CSS555 Demo Kit to program the CSS555C for a guitar tuner. This review can be found on the science20.com website. CSS was invited to the ON Semiconductors Executive Summit in Scottsdale, Arizona, an event that allows ON's major customers to engage with ON Executives for productive collaboration discussions. The summit commenced on January 29 with an overview and dinner meeting featuring speakers such as Keith Jackson, President and CEO, and Bob Mahoney, Executive Vice President of Sales and Marketing. Customer breakout sessions began the following day, with CSS represented by executives John Cheng and Mike McDaid. ON Semi Executives included Rocke Acree, Mike Kenyon, Chip Brakeville, and Abdi Afshar. At the meeting, John Cheng highlighted the advantages of the CSS/Chronicle merger, including an expanded engineering workforce and enhanced production and testing capabilities. Another significant topic was the development of EEPROM technology for the ON Semi ONC18 process (180 nm) at the Gresham facility, with CSS leading the design and evaluation while ON handles silicon fabrication. Test structures for EEPROM cells and associated circuits have been completed and are set to enter fabrication at ON. This will be followed by the development of a complete EEPROM memory and necessary on-chip programming circuits. Following the meetings, ON hosted an event at the Phoenix Open, where CSS executives enjoyed refreshments and observed Phil Mickelson's near-record-breaking round. Chronicle Technology has recently completed ESD and life testing of its motion control ASIC, clearing the way for production volume ramp-up. This custom-designed mixed-signal ASIC is intended for a flagship consumer product of a publicly traded company, controlling multiple motors for various operations, including forward/reverse and variable speed/torque. It also features 200 general-purpose instrumentation amplified sensor inputs, battery charge management, voltage level sensing, a temperature sensor, an internal RC oscillator, a watchdog timer, and an LDO regulator. The motor operating voltage range is 5V to 35V, while the rest of the chip operates between 3V to 5V. All control and data are accessible through a 10 MHz SPI bus, and the component is packaged in a 68-pin QFN package. This ASIC is similar to many other designs at Chronicle and CSS, which specialize in custom mixed-signal ASICs for control and instrumentation applications across various markets. Contact information for inquiries regarding mixed-signal ASIC suitability for specific applications is provided. Custom Silicon Solutions (CSS) and Chronicle Technology's ASIC division merged on January 1, 2013, continuing to operate as CSS. This merger significantly enhances the design bandwidth and depth of mixed-signal ASIC design capability. Chronicle's design team complements CSS's with extensive experience in high-performance circuits across Digital, Analog, Mixed-Signal, Image Sensor, and RF applications utilizing various process technologies. Foundry experience now encompasses ON Semi, Tower Jazz, XFab, Atmel, IBM, Global, UMC, SMIC, and TSMC, with dimensions ranging from 65 nm to 1.25 microns. Chronicle Technology has provided advanced IC designs for 17 years, completing over 200 tape-outs for clients in Industrial, Medical, Military, and Commercial markets. CSS has been operating for a similar duration, serving comparable markets. CSS has a strong track record of shipping tested, packaged ASICs, while Chronicle's team possesses extensive design expertise in advanced integrated technologies. The new CSS will offer a broader range of Custom Turn-Key ASIC Solutions from Development through Production. A video detailing the features of the CSS555 Timer IC and the CSS555 Demonstration Kit is available on YouTube. For inquiries about the CSS555 Timer or Demo Kit, contact information is provided, along with a link to the website where both products can be purchased. CSS employees have a long history in non-volatile memory development, with foundational work in the late 1970s at Hughes Research Center, where Dr. Eli Harari developed EEPROM fundamentals using Fowler-Nordheim tunneling. This technology was proven practical for integrated technology, with significant contributions from the team, including the development of test structures and enhancements in EEPROM design for improved yield and reliability. The evolution of EEPROM technology at Hughes led to significant advancements, including redundancy and internal programming voltage generation, resulting in higher production yields and reliability. Ongoing development efforts have continued to advance EEPROM technology, ensuring that contemporary manufacturing processes yield higher quality tunnel oxides, eliminating the need for extensive pre-sale testing protocols.I read Doug Grant`s article regarding Heathkit in his Blog via the EDN Network. Doug reminisced about building his first Heathkit and how much he learned. He suggested that every EE had at least one kit and I suspect he is right. However, as Doug pointed out, Heathkit eventually faded away. I built a number of kits, including an oscilloscope, a so lid-state FM tuner and amplifier and a color TV. All worked fine and found lots of use. But the real advantage was the first-hand learning experience & knowledge gained in building the kits. The building instructions were always clear and the circuit operation explanations were my first real learning experience in electronics.

Just learning how to solder was a valuable experience! Doug`s Blog provides a link to someone who may be considering offering the kits again and he also offers his suggestion for a new kit. A lot of comments follow the Blog offering individual experiences with Heathkit and related suggestions.

I feel that they offered an excellent product for that time period and I am glad I had the opportunity to learn by building their kits. CSS Engineers have teamed with Sarnoff/SRI in the design of a CMOS image sensor that is slated to be aboard the Naval Research Laboratory s Solar Orbiter Heliospheric Imager (SoloHI).

This work is a continuation of a long teaming relationship with Sarnoff, having completed 16 earlier tape-outs of new designs. This will be the first time such a large format APS detector has flown. The instrument will make high-resolution images of the corona and solar wind, including coronal mass ejections (CMEs), to determine how they propagate and interact with the background solar wind.

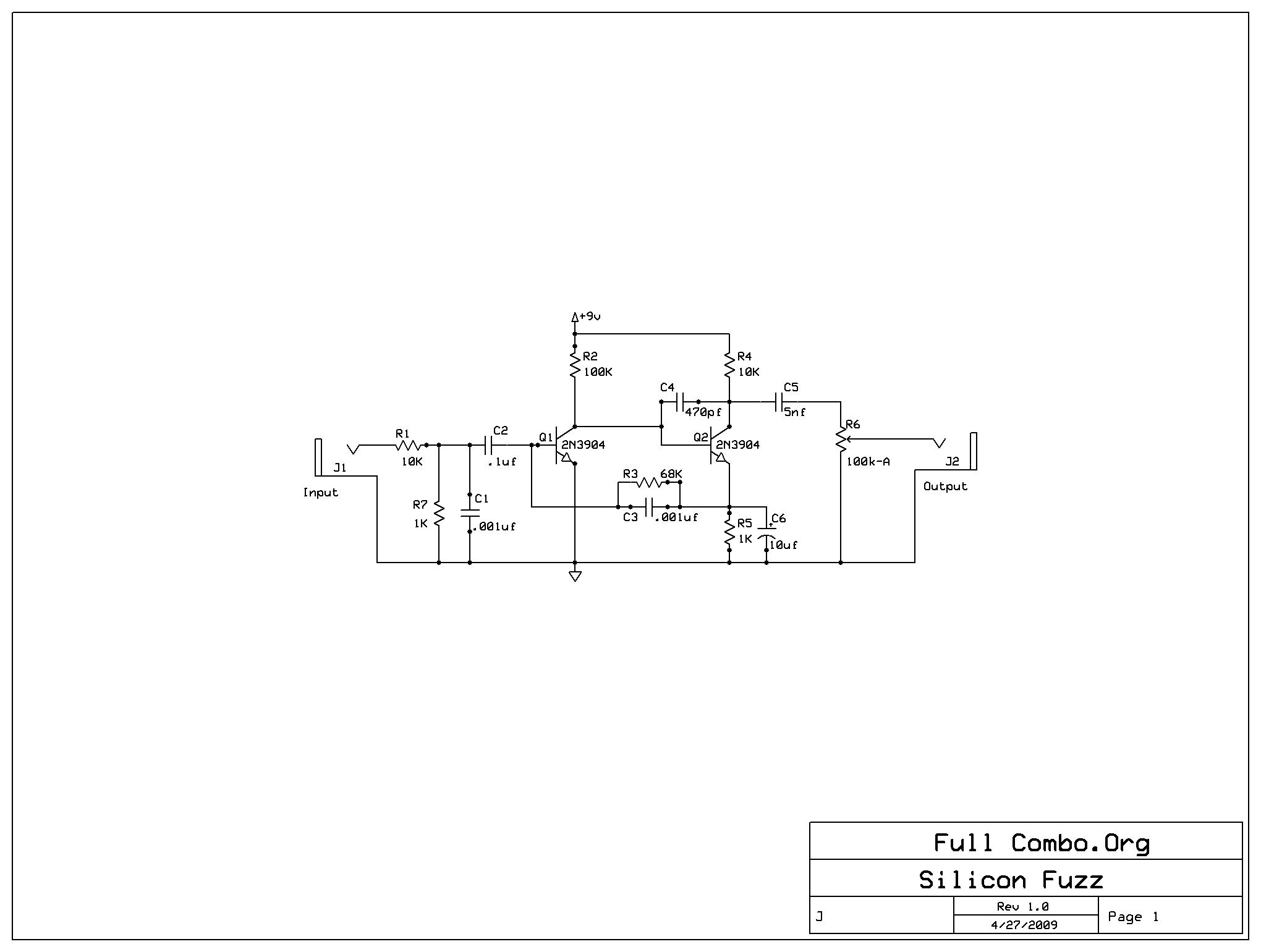

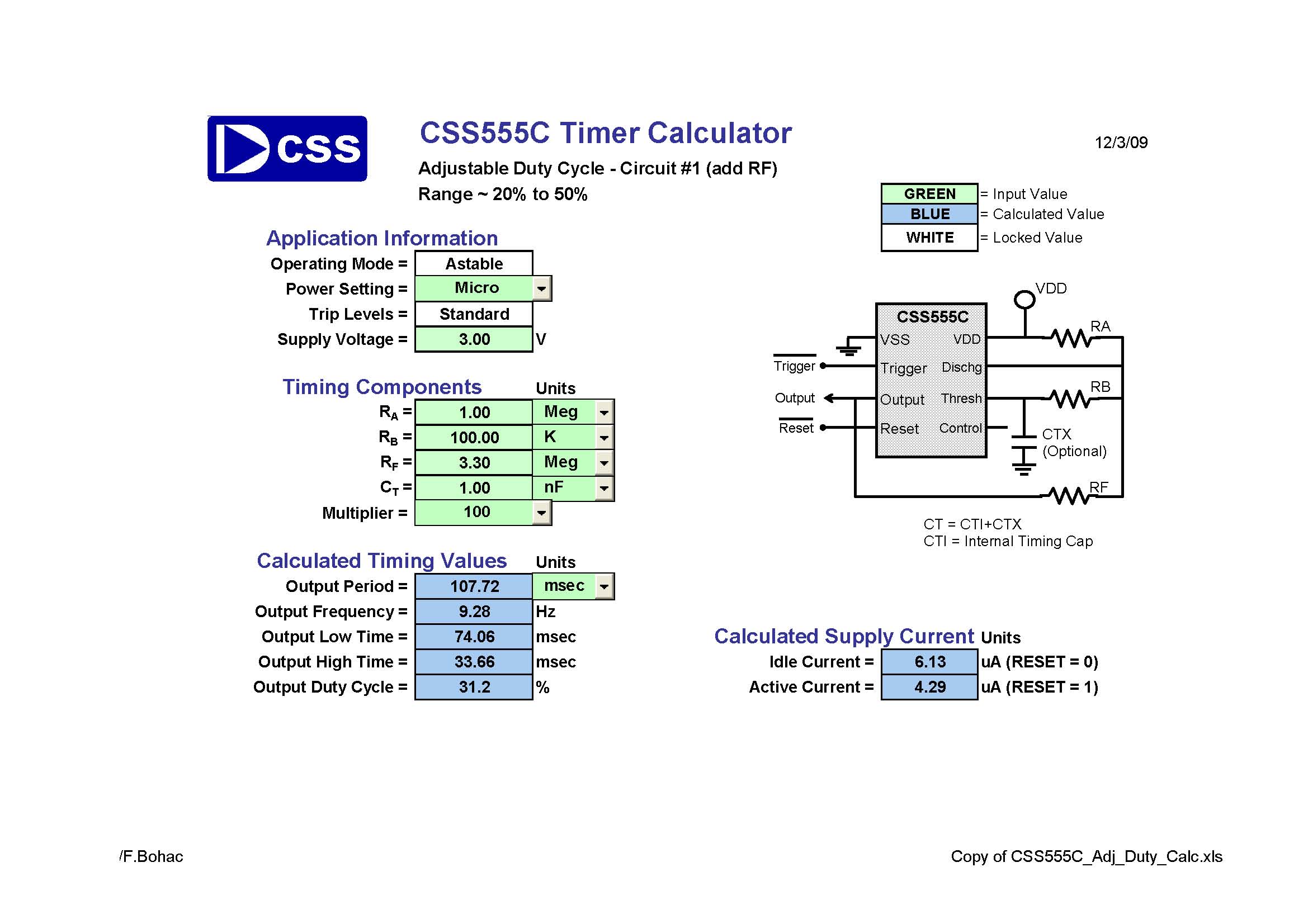

With its large field of view, SoloHI will be able to connect the remote sensing observations of the corona to the plasma being measured in-situ at the spacecraft. I read a very nice review of an application of the CSS555 Timer IC by Steve Schuler from his BLOG Square_Root_of_Not.

Steve shows how to use the CSS555 Demo Kit to program the CSS555C to set the frequencies for a guitar tuner. Check out the review on the science20. com website. Custom Silicon Solutions (CSS) was again invited to attend the ON Semiconductors Executive Summit in Scottsdale, Arizona.

This annual event provides an opportunity for ON`s major customers to meet one-on-one with ON Executives and discuss how to work together more productively. The event began Tuesday evening (January 29) with the ON Semiconductor Executive Overview & Dinner Meeting.

Speakers included Keith Jackson, President, Chief Executive Officer and Director, Bob Mahoney, Executive Vice President, Sales and Marketing, and David Somo, Vice President, Corporate Marketing. The Customer Breakout Sessions (one-on-one discussions between ON Semi and Customer Executives) began on Wednesday.

CSS (now merged with Chronicle Technology) was represented by CSS Executives John Cheng and Mike McDaid. ON Semi Executives included Rocke Acree (Custom Foundry Business Unit Manager), Mike Kenyon (Sales Director, Western US), Chip Brakeville (Regional Sales Manager, Southwest & Central US and South America) and Abdi Afshar (Field Application Engineer).

At the meeting, John Cheng discussed the benefits of the CSS/Chronicle Merger, including the significantly increased engineering staff and the additional production & testing capabilities of the combined companies. Another topic of special interest was the development of EEPROM technology for the ON Semi ONC18 process (180 nM process at the ON Gresham facility).

CSS is developing this technology (design & evaluation) with ON providing silicon fabrication. Test structures for EEPROM cells & associated circuits have been completed and are soon to begin fabrication at ON. This will be followed by development of a complete EEPROM memory and the required on-chip programming circuits.

As a special treat following these meetings on Thursday, ON hosted the opening day at the Phoenix Open at their corporate tent on the 9th green. John and Mike from CSS attended and were able to enjoy refreshments at the tent and then follow Phil Mickelson around the course in his near record breaking round.

Chronicle Technology has just recently completed ESD and life testing of its motion control ASIC, which now clears the path for production volume ramp-up. This custom designed mixed-signal ASIC is targeted for a publicly traded company`s flag ship consumer product.

The ASIC controls multiple motors for forward / reverse / variable speed / variable torque operations. Also included are 200 general purpose instrumentation amplified sensor inputs, battery charge management, voltage level sensing, a temperature sensor, an internal RC oscillator, a watchdog timer and an LDO regulator.

The motor operating Voltage range is between 5V to 35V, while the rest of the chip can operate between 3V to 5V. All control and data are available through a 10 MHz SPI bus. The part is packaged in a 68 pin QFN package. This ASIC is similar to many others designed at Chronicle and CSS. We specialize in custom mixed-signal ASICs for control and instrumentation applications in a variety of markets.

Please contact Mike McDaid to answer any questions you may have and help you decide if a mixed-signal ASIC is right for you and your application. We have some great news! Custom Silicon Solutions (CSS) and Chronicle Technology`s ASIC division completed a merger as of Jan 1st, 2013.

The newly combined company will continue to operate as CSS. The merger greatly increases the design bandwidth and depth of the mixed signal ASIC design capability. Chronicle`s design team complements the CSS design team with many years of experience designing state-of-the-art, high performance circuits in Digital, Analog, Mixed-Signal, Image Sensor, and RF applications utilizing CMOS, SiGe, BiCMOS, BiPolar, CIS, and SOI process technologies.

Foundry experience now includes ON Semi, Tower Jazz, XFab, Atmel, IBM, Global, UMC, SMIC, and TSMC in dimensions from 65 nm to 1. 25 micron. Chronicle Technology has been providing advanced IC designs for 17 years, producing over 200 tape-outs for clients in the Industrial, Medical, Military and Commercial markets.

Coincidentally, CSS has also been in business for about the same time (both were founded in 1996) serving similar markets. CSS has an extensive track record for shipping tested, packaged ASICs, while Chronicle`s team has extensive design expertise in advanced integrated technologies.

The new CSS will be able to provide a broader range of Custom Turn-Key ASIC Solutions from Development through Production. We have recently published a video on YouTube which briefly explains the features of our CSS555 Timer IC and the use of the CSS555 Demonstration Kit for that Timer IC.

Please follow this link and take a look. If you have an interest in the CSS555 Timer or Demo Kit you may want to contact Mike McDaid at CSS (MMcDaid@CustomSiliconSolutions. com) or visit our website under Standard Products. Both the CSS555 and the CSS555 Demo Kit are available for purchase from. CSS employees have a long history in the development and use of non-volatile memory. Frank Bohac and I began our non-volatile memory work in the late 70`s at the Hughes Research Center in Newport Beach, California.

At that time, Dr. Eli Harari was at the Hughes Newport Research center developing the fundamentals of EEPROMs using Fowler-Nordheim tunneling to erase and program floating gate non-volatile memories. Eli was to prove that this fundamental technology was practical for integrated technology. To prove this, Eli used a tester that I had developed that would easily test thousands of tunnel oxides to establish their characteristics.

Thus, he and I became acquainted and soon afterwards, I began working on the floating gate EEPROM development, as well. Eli successfully filed many patents establishing this basic technology as practical in the fabrication of floating gate non-volatile memories, with the seminal paper Dielectric Breakdown in Electrically Stressed Thin Films on Thermal SiO2 .

(link: Also, see our earlier Blog (September 2012) on the IEEE Significant Event Award recently presented to Dr. Harari. This early EEPROM development was shown in a poster at the Flash Memory Summit recently held in Santa Clara.

Below, a portion of the poster indicates the work completed at the Hughes Research Center from 1976 to 1980. Dr. Tom Tombs, then the director of the Hughes Research Center, asked if I would take this EEPROM technology and develop it to a production level at the Hughes Microelectronics Division (also in Newport Beach).

An 8K bit EEPROM CMOS memory (originally designed by Frank Wanlass under contract by Hughes) was used as a vehicle to prove production capability. At Hughes Microelectronics, I worked with process development engineers (primarily Bruce Paynter) in a variety of process experiments aimed at improving what was initially a dismal yield on the 8K bit EEPROM.

The primary breakthrough was the realization that Nitrogen used to control the start and termination of the tunnel oxide growth had a detrimental effect on tunnel oxide yield and endurance characteristics. By removing Nitrogen from the process we were able to significantly improve tunnel oxide yield. Another significant realization was that the peak magnitude of the tunnel oxide current needed to be carefully controlled to prevent early breakdown of the oxide.

We found that through careful control of the rise time of the voltage used to program the EEPROM we could avoid this oxide damage. I presented the development of the 8K EEPROM at the Non-volatile Memory Workshop held in 1980 in Vail, Colorado.

The paper was well received with a torrent of questions following the presentation. I also wrote an article describing the 8K bit EEPROM entitled: Low-Power EEPROM Can Be Re-programmed Fast in the July 31, 1980 issue of Electronics magazine. These papers presented an overview of the basic non-volatile functions of these memories. Frank Bohac joined the development team at Hughes Microelectronics and became the key designer of changes to the CMOS EEPROM.

Frank fixed some problems with the initial EEPROM design which were unrelated to the non-volatile memory (latch-up) and provided memory maps that led us to determine the effects of tunnel oxide shorts on adjacent cells. However, the first major change was the addition of redundancy to the EEPROM. Even though yield of the tunnel oxides was reasonably good with the above developments, a large number of devices were failing (due to tunnel oxide failures) either initially or after a few programming cycles.

We determined that just a few bits of redundancy were needed to fabricate the 8K EEPROMs with acceptable yields. Frank also added internal program voltage generation to the EEPROM. This internal program voltage generator provided for a nearly ideal voltage rise time which reduced peak tunnel oxide current and hence reduced tunnel oxide failures.

Frank successfully redesigned the 8K EEPROM to include both redundancy and an internal program voltage generator. These additions brought the EEPROM yields to an acceptable production level. Frank also presented a paper at a later Nonvolatile Memory Workshop which described the redundancy used in the 8K EEPROM at Hughes as well as the details of the programming voltage generator waveform used in this memory.

We also determined that for reliability it was necessary to repeatedly program and erase the EEPROM prior to sale to remove any tunnel oxides with apparent latent defects. (The failed cells were replaced with good cells via the redundancy circuitry). Although this was a time consuming and expensive process (10K cycles at 125 degrees C), it was believed necessary (with the quality of oxides at that time) for a high reliability device.

Today, tunnel oxides at our foundries are of much higher quality and such screening techniques are not required. During this period of time, Hughes won a contract from ERADCOM to evaluate the floating gate non-volatile memory technology available on the market.

Bruce Paynter, Frank Bohac and I performed this work by evaluating the endurance and retention characteristics of EEPROM memories available from Intel, National and Hughes. This was an in-depth analysis of EEPROMs, establishing for the first time significant data on the technology`s endurance and retention characteristics.

Long term endurance and retention characteristics have not changed a lot since that time as long as the fundamentals of the Fowler-Nordheim tunneling characteristics are observed. EEPROM development at Hughes continued with a 16K bit EEPROM and a non-volatile RAM IC (NovRAM). Howev 🔗 External reference

Just learning how to solder was a valuable experience! Doug`s Blog provides a link to someone who may be considering offering the kits again and he also offers his suggestion for a new kit. A lot of comments follow the Blog offering individual experiences with Heathkit and related suggestions.

I feel that they offered an excellent product for that time period and I am glad I had the opportunity to learn by building their kits. CSS Engineers have teamed with Sarnoff/SRI in the design of a CMOS image sensor that is slated to be aboard the Naval Research Laboratory s Solar Orbiter Heliospheric Imager (SoloHI).

This work is a continuation of a long teaming relationship with Sarnoff, having completed 16 earlier tape-outs of new designs. This will be the first time such a large format APS detector has flown. The instrument will make high-resolution images of the corona and solar wind, including coronal mass ejections (CMEs), to determine how they propagate and interact with the background solar wind.

With its large field of view, SoloHI will be able to connect the remote sensing observations of the corona to the plasma being measured in-situ at the spacecraft. I read a very nice review of an application of the CSS555 Timer IC by Steve Schuler from his BLOG Square_Root_of_Not.

Steve shows how to use the CSS555 Demo Kit to program the CSS555C to set the frequencies for a guitar tuner. Check out the review on the science20. com website. Custom Silicon Solutions (CSS) was again invited to attend the ON Semiconductors Executive Summit in Scottsdale, Arizona.

This annual event provides an opportunity for ON`s major customers to meet one-on-one with ON Executives and discuss how to work together more productively. The event began Tuesday evening (January 29) with the ON Semiconductor Executive Overview & Dinner Meeting.

Speakers included Keith Jackson, President, Chief Executive Officer and Director, Bob Mahoney, Executive Vice President, Sales and Marketing, and David Somo, Vice President, Corporate Marketing. The Customer Breakout Sessions (one-on-one discussions between ON Semi and Customer Executives) began on Wednesday.

CSS (now merged with Chronicle Technology) was represented by CSS Executives John Cheng and Mike McDaid. ON Semi Executives included Rocke Acree (Custom Foundry Business Unit Manager), Mike Kenyon (Sales Director, Western US), Chip Brakeville (Regional Sales Manager, Southwest & Central US and South America) and Abdi Afshar (Field Application Engineer).

At the meeting, John Cheng discussed the benefits of the CSS/Chronicle Merger, including the significantly increased engineering staff and the additional production & testing capabilities of the combined companies. Another topic of special interest was the development of EEPROM technology for the ON Semi ONC18 process (180 nM process at the ON Gresham facility).

CSS is developing this technology (design & evaluation) with ON providing silicon fabrication. Test structures for EEPROM cells & associated circuits have been completed and are soon to begin fabrication at ON. This will be followed by development of a complete EEPROM memory and the required on-chip programming circuits.

As a special treat following these meetings on Thursday, ON hosted the opening day at the Phoenix Open at their corporate tent on the 9th green. John and Mike from CSS attended and were able to enjoy refreshments at the tent and then follow Phil Mickelson around the course in his near record breaking round.

Chronicle Technology has just recently completed ESD and life testing of its motion control ASIC, which now clears the path for production volume ramp-up. This custom designed mixed-signal ASIC is targeted for a publicly traded company`s flag ship consumer product.

The ASIC controls multiple motors for forward / reverse / variable speed / variable torque operations. Also included are 200 general purpose instrumentation amplified sensor inputs, battery charge management, voltage level sensing, a temperature sensor, an internal RC oscillator, a watchdog timer and an LDO regulator.

The motor operating Voltage range is between 5V to 35V, while the rest of the chip can operate between 3V to 5V. All control and data are available through a 10 MHz SPI bus. The part is packaged in a 68 pin QFN package. This ASIC is similar to many others designed at Chronicle and CSS. We specialize in custom mixed-signal ASICs for control and instrumentation applications in a variety of markets.

Please contact Mike McDaid to answer any questions you may have and help you decide if a mixed-signal ASIC is right for you and your application. We have some great news! Custom Silicon Solutions (CSS) and Chronicle Technology`s ASIC division completed a merger as of Jan 1st, 2013.

The newly combined company will continue to operate as CSS. The merger greatly increases the design bandwidth and depth of the mixed signal ASIC design capability. Chronicle`s design team complements the CSS design team with many years of experience designing state-of-the-art, high performance circuits in Digital, Analog, Mixed-Signal, Image Sensor, and RF applications utilizing CMOS, SiGe, BiCMOS, BiPolar, CIS, and SOI process technologies.

Foundry experience now includes ON Semi, Tower Jazz, XFab, Atmel, IBM, Global, UMC, SMIC, and TSMC in dimensions from 65 nm to 1. 25 micron. Chronicle Technology has been providing advanced IC designs for 17 years, producing over 200 tape-outs for clients in the Industrial, Medical, Military and Commercial markets.

Coincidentally, CSS has also been in business for about the same time (both were founded in 1996) serving similar markets. CSS has an extensive track record for shipping tested, packaged ASICs, while Chronicle`s team has extensive design expertise in advanced integrated technologies.

The new CSS will be able to provide a broader range of Custom Turn-Key ASIC Solutions from Development through Production. We have recently published a video on YouTube which briefly explains the features of our CSS555 Timer IC and the use of the CSS555 Demonstration Kit for that Timer IC.

Please follow this link and take a look. If you have an interest in the CSS555 Timer or Demo Kit you may want to contact Mike McDaid at CSS (MMcDaid@CustomSiliconSolutions. com) or visit our website under Standard Products. Both the CSS555 and the CSS555 Demo Kit are available for purchase from. CSS employees have a long history in the development and use of non-volatile memory. Frank Bohac and I began our non-volatile memory work in the late 70`s at the Hughes Research Center in Newport Beach, California.

At that time, Dr. Eli Harari was at the Hughes Newport Research center developing the fundamentals of EEPROMs using Fowler-Nordheim tunneling to erase and program floating gate non-volatile memories. Eli was to prove that this fundamental technology was practical for integrated technology. To prove this, Eli used a tester that I had developed that would easily test thousands of tunnel oxides to establish their characteristics.

Thus, he and I became acquainted and soon afterwards, I began working on the floating gate EEPROM development, as well. Eli successfully filed many patents establishing this basic technology as practical in the fabrication of floating gate non-volatile memories, with the seminal paper Dielectric Breakdown in Electrically Stressed Thin Films on Thermal SiO2 .

(link: Also, see our earlier Blog (September 2012) on the IEEE Significant Event Award recently presented to Dr. Harari. This early EEPROM development was shown in a poster at the Flash Memory Summit recently held in Santa Clara.

Below, a portion of the poster indicates the work completed at the Hughes Research Center from 1976 to 1980. Dr. Tom Tombs, then the director of the Hughes Research Center, asked if I would take this EEPROM technology and develop it to a production level at the Hughes Microelectronics Division (also in Newport Beach).

An 8K bit EEPROM CMOS memory (originally designed by Frank Wanlass under contract by Hughes) was used as a vehicle to prove production capability. At Hughes Microelectronics, I worked with process development engineers (primarily Bruce Paynter) in a variety of process experiments aimed at improving what was initially a dismal yield on the 8K bit EEPROM.

The primary breakthrough was the realization that Nitrogen used to control the start and termination of the tunnel oxide growth had a detrimental effect on tunnel oxide yield and endurance characteristics. By removing Nitrogen from the process we were able to significantly improve tunnel oxide yield. Another significant realization was that the peak magnitude of the tunnel oxide current needed to be carefully controlled to prevent early breakdown of the oxide.

We found that through careful control of the rise time of the voltage used to program the EEPROM we could avoid this oxide damage. I presented the development of the 8K EEPROM at the Non-volatile Memory Workshop held in 1980 in Vail, Colorado.

The paper was well received with a torrent of questions following the presentation. I also wrote an article describing the 8K bit EEPROM entitled: Low-Power EEPROM Can Be Re-programmed Fast in the July 31, 1980 issue of Electronics magazine. These papers presented an overview of the basic non-volatile functions of these memories. Frank Bohac joined the development team at Hughes Microelectronics and became the key designer of changes to the CMOS EEPROM.

Frank fixed some problems with the initial EEPROM design which were unrelated to the non-volatile memory (latch-up) and provided memory maps that led us to determine the effects of tunnel oxide shorts on adjacent cells. However, the first major change was the addition of redundancy to the EEPROM. Even though yield of the tunnel oxides was reasonably good with the above developments, a large number of devices were failing (due to tunnel oxide failures) either initially or after a few programming cycles.

We determined that just a few bits of redundancy were needed to fabricate the 8K EEPROMs with acceptable yields. Frank also added internal program voltage generation to the EEPROM. This internal program voltage generator provided for a nearly ideal voltage rise time which reduced peak tunnel oxide current and hence reduced tunnel oxide failures.

Frank successfully redesigned the 8K EEPROM to include both redundancy and an internal program voltage generator. These additions brought the EEPROM yields to an acceptable production level. Frank also presented a paper at a later Nonvolatile Memory Workshop which described the redundancy used in the 8K EEPROM at Hughes as well as the details of the programming voltage generator waveform used in this memory.

We also determined that for reliability it was necessary to repeatedly program and erase the EEPROM prior to sale to remove any tunnel oxides with apparent latent defects. (The failed cells were replaced with good cells via the redundancy circuitry). Although this was a time consuming and expensive process (10K cycles at 125 degrees C), it was believed necessary (with the quality of oxides at that time) for a high reliability device.

Today, tunnel oxides at our foundries are of much higher quality and such screening techniques are not required. During this period of time, Hughes won a contract from ERADCOM to evaluate the floating gate non-volatile memory technology available on the market.

Bruce Paynter, Frank Bohac and I performed this work by evaluating the endurance and retention characteristics of EEPROM memories available from Intel, National and Hughes. This was an in-depth analysis of EEPROMs, establishing for the first time significant data on the technology`s endurance and retention characteristics.

Long term endurance and retention characteristics have not changed a lot since that time as long as the fundamentals of the Fowler-Nordheim tunneling characteristics are observed. EEPROM development at Hughes continued with a 16K bit EEPROM and a non-volatile RAM IC (NovRAM). Howev 🔗 External reference