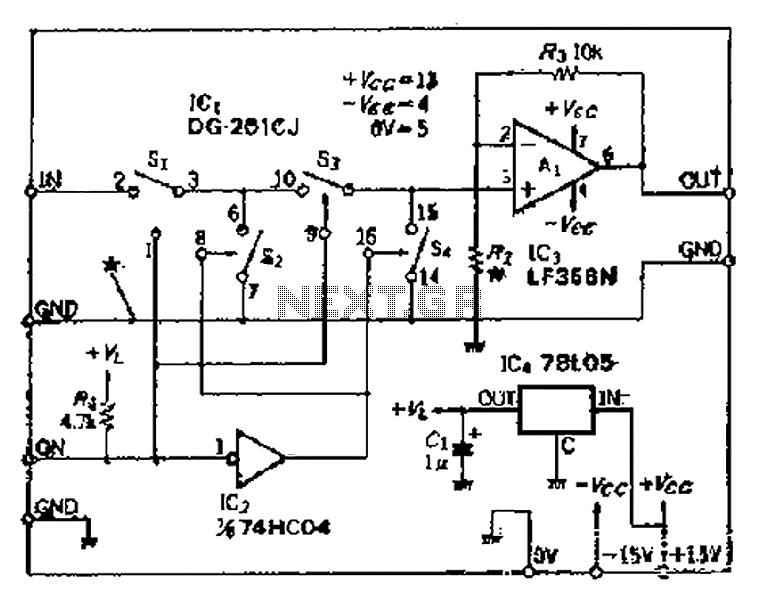

Cutting good performance signal switching circuit

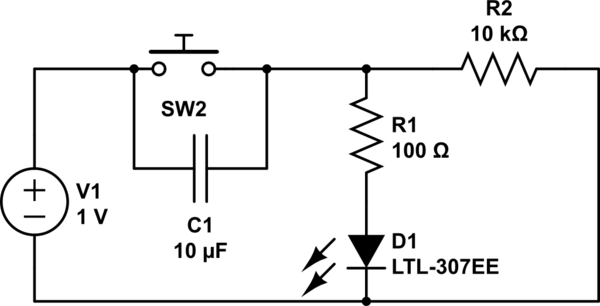

Analog switches SL and SA disconnect the inverted logic signal to terminal 2. S1 and S4 are turned on, allowing capacitance between S1 and S8 to couple. S2 and S4 shunt with an on-state resistance ranging from 50 to 100 ohms. An operational buffer amplifier is utilized, and the resistor R2 should be selected based on the availability of several components, where the voltage gain is 4.1 +/- 1.

The circuit involves the use of analog switches SL and SA, which are crucial for controlling the flow of signals based on the logic state. When the inverted logic signal is applied to terminal 2, it activates switches S1 and S4, creating a path for capacitance coupling between S1 and S8. This configuration is essential for ensuring that the signals can interact without direct electrical connection, thereby maintaining isolation while allowing for signal transmission.

The on-state resistance of the switches, which is specified to be between 50 and 100 ohms, plays a significant role in determining the overall signal integrity and performance of the circuit. Lower on-state resistance typically results in reduced power loss and improved signal fidelity.

Additionally, the operational buffer amplifier serves to isolate the input from the output, providing a high input impedance and low output impedance. This characteristic is vital for preventing loading effects on the previous stage of the circuit. The choice of resistor R2 should be made considering the availability of components and the desired voltage gain, which is specified as 4.1 +/- 1. This gain setting can be critical for applications requiring specific signal levels, ensuring that the output remains within acceptable limits for further processing or interfacing with other circuit stages.

Overall, the described circuit configuration is designed to facilitate efficient signal management while maintaining the necessary performance characteristics through careful selection of components and design parameters.Analog switches sl and sa disconnect, Ctz the inverted logic signal to terminal 2 s! And 84 is turned on, so that prisoners capacitance between S1 and S 8 and coupling will be generated and S 2 and 8 4 shunt (on-state resistance 50 ~ lOOQ). OP buffer amplifier is a buffer amplifier. Rz need to choose according to the availability of several scrimp 4 1 +/l where the voltage gain.

The circuit involves the use of analog switches SL and SA, which are crucial for controlling the flow of signals based on the logic state. When the inverted logic signal is applied to terminal 2, it activates switches S1 and S4, creating a path for capacitance coupling between S1 and S8. This configuration is essential for ensuring that the signals can interact without direct electrical connection, thereby maintaining isolation while allowing for signal transmission.

The on-state resistance of the switches, which is specified to be between 50 and 100 ohms, plays a significant role in determining the overall signal integrity and performance of the circuit. Lower on-state resistance typically results in reduced power loss and improved signal fidelity.

Additionally, the operational buffer amplifier serves to isolate the input from the output, providing a high input impedance and low output impedance. This characteristic is vital for preventing loading effects on the previous stage of the circuit. The choice of resistor R2 should be made considering the availability of components and the desired voltage gain, which is specified as 4.1 +/- 1. This gain setting can be critical for applications requiring specific signal levels, ensuring that the output remains within acceptable limits for further processing or interfacing with other circuit stages.

Overall, the described circuit configuration is designed to facilitate efficient signal management while maintaining the necessary performance characteristics through careful selection of components and design parameters.Analog switches sl and sa disconnect, Ctz the inverted logic signal to terminal 2 s! And 84 is turned on, so that prisoners capacitance between S1 and S 8 and coupling will be generated and S 2 and 8 4 shunt (on-state resistance 50 ~ lOOQ). OP buffer amplifier is a buffer amplifier. Rz need to choose according to the availability of several scrimp 4 1 +/l where the voltage gain.