Deeply embedded design

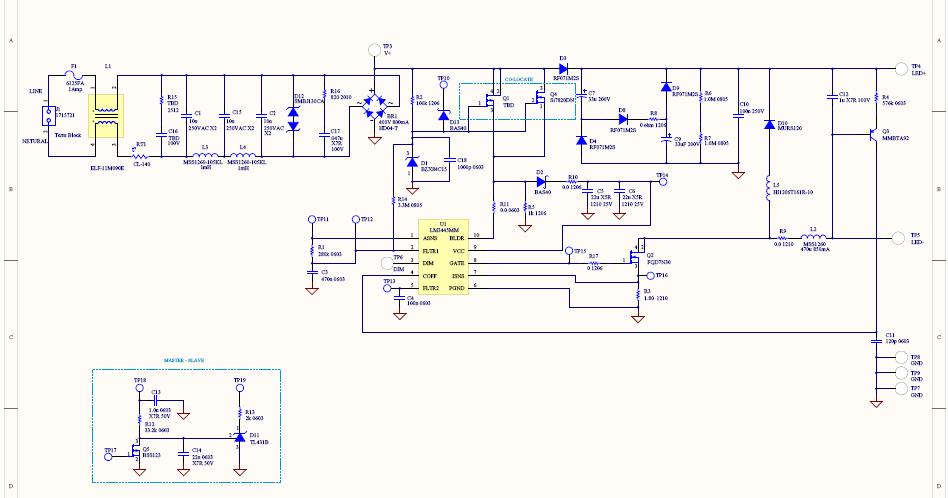

The following is an account of such an undertaking. Recently, a design review was conducted for a cost reduction project where an older design was updated. The new design merged two different designs, incorporating some updated components alongside existing controls. The configuration features six 10 Amp H-bridge drivers and the associated control logic. Initial testing revealed significant current spikes and higher than desirable levels of electromagnetic interference (EMI). A consultant who assisted with similar designs, particularly regarding EMI issues, suggested several timing modifications to the circuitry. During discussions, two distinct timing schemes were proposed. A suggestion was made to replace the entire control circuitry with a small microprocessor or a Complex Programmable Logic Device (CPLD), which would provide flexibility in adjusting the timing schemes. Although initially met with skepticism, further discussions confirmed the feasibility and potential benefits of this approach. The desired control level and various delay ranges were subsequently defined. Before proceeding, a thorough analysis of the current circuit was planned to assess its functionality and actual delay times to establish a baseline. The overall circuit design is straightforward; changes in the 'Direction' line necessitate precise sequencing of the current source and bridge drivers. Upon a direction change, the currently selected drivers (opposite side, top and bottom MOSFETs) are disabled alongside the programmable current source, followed by a delay before enabling the opposite MOSFETs and another delay before reactivating the current source. The sequence and timing of these operations significantly influence the performance and EMI characteristics of the six H-bridges. The schematic includes two delay circuits (two copies using 10K and 0.1µF, plus one using 10 and 3.9µF). The direction control circuits utilize two different inverters (an open collector type - SN7406 and a Schmitt trigger type - 74HTC14). Each inverter manages different edges of the transitions: the Schmitt trigger controls the rising edge (enable) by charging a timing capacitor (0.1µF) through a series resistor to create a fixed delay, while the open collector inverter manages the falling edge (disable) by rapidly discharging the capacitor to achieve a near-zero delay turn-off. This combination of inverter types is an effective strategy, as the Schmitt trigger provides a drive of approximately 4mA for both high and low states, while the open collector device can sink around 40mA during the low state, ensuring controlled rise times and fast fall times. The second delay circuit is responsible for controlling the programmable current source by temporarily disabling it during direction changes.

The design of the H-bridge driver circuit is critical for applications requiring precise motor control, such as robotics and automation systems. The six 10 Amp H-bridge drivers are configured to manage the direction and speed of DC motors efficiently. By employing a microprocessor or CPLD for control logic, the design allows for programmable features such as acceleration profiles, dynamic braking, and fault detection, enhancing the overall performance and reliability of the system.

The integration of timing circuits within the control logic is essential for minimizing EMI, which can adversely affect nearby electronic devices. The use of a Schmitt trigger inverter for the rising edge ensures a clean transition, reducing the risk of false triggering due to noise. The fast discharge capability of the open collector inverter on the falling edge contributes to rapid turn-off times, minimizing the duration of high current spikes that can lead to EMI.

The choice of timing components, such as the capacitors and resistors, directly influences the delay characteristics of the circuit. The values selected (10KΩ with 0.1µF and 10Ω with 3.9µF) provide a balance between responsiveness and stability, allowing for fine-tuning of the delays to optimize performance. The design must also consider thermal management, as the high-current operation of the H-bridge drivers generates heat, which must be dissipated effectively to prevent component failure.

In conclusion, the proposed design revision not only addresses the immediate concerns of current spikes and EMI but also enhances the overall functionality and adaptability of the H-bridge driver circuit. By leveraging modern microprocessor or CPLD technology, the design can evolve to meet future requirements while maintaining robust performance in demanding applications.The following is an account of such an undertaking. Recently I was involved in a design review for a cost reduction project, where an older design was getting an update. The new design was a merging of two different designs, including someupdated parts and some existing controls.

The design includes six 10Amp H-bridge drivers and the associated control logic. Some of the early testing had shown some rather large current spikes and also some higher than desirable amounts of electromagnetic interference (EMI). A consultant who had been helping out on a similar design, mostly on EMI concerns, had suggested a few timing changes to the circuitry.

As the talks continued, two different schemes involving changes to the timing were discussed. At this point, I had jumped in and suggested that we pull out all the control circuitry and replace it with a small microprocessor or a CPLD, allowing us some freedom to make changes in the timing schemes. My manager had referred to my suggestion as "a small joke", but I assured him I was serious. A couple of days later I met with my manager and we talked a little more about the idea of handling the bridge control logic inside of a small microprocessor.

After we are able to agree that it would in fact be possible (and also a good idea to do so), we quickly defined the desired level of control and the range of the different delays that we would need to consider. Great, we have a plan and a direction. Before we jump into the work, let`s take a moment and analyze the current circuit to determine present functionality and the actual delay times in order to better understand our starting point.

The big picture view on the circuit is actually quite simple. Changes in the `Direction` line require proper sequencing of the current source and the bridge drivers. On a change in direction, the presently selected drivers (opposite side, top and bottom MOSFETs) are disabled along with the programmable current source.

Then a delay occurs before enabling the opposite set of MOSFETs, along with another delay prior to re-enabling the current source. It is the sequence of these actions and the time delays that will have effects on the operation and resulting EMI characteristics of our six H-bridges.

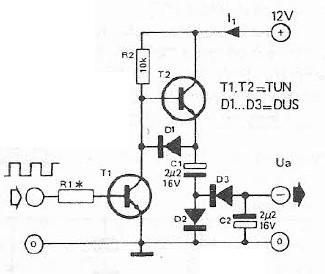

In the above schematic there are two different delay circuits (two copies using 10K and 0. 1uF, plus one using 10 and 3. 9uF). The direction control circuits each use two different inverters (an open collector type - SN7406 and a Schmitt trigger type - 74HTC14). Each of these inverters are use to control a different edge of the transitions, the Schmitt trigger controls the rising edge (enable), by applying a charging current through a series resistor into a timing capacitor (0.

1uF) to cause a fixed delay, while the open collector inverter controls the falling edge (disable), by using a high current dump of the charge on the capacitor to effect a near zero delay turn off. The combination of the two inverter types is actually a clever approach. The Schmitt trigger device drives both high and low at ~4ma, while the Open Collector device provides no drive in high, but can sink ~40ma during the low state, providing controlled rise time and fast fall time.

The second delay circuit is used to control the programmable current source by temporarily disabling the current source during the direction changes. This stage uses a single Open Collecto 🔗 External reference

The design of the H-bridge driver circuit is critical for applications requiring precise motor control, such as robotics and automation systems. The six 10 Amp H-bridge drivers are configured to manage the direction and speed of DC motors efficiently. By employing a microprocessor or CPLD for control logic, the design allows for programmable features such as acceleration profiles, dynamic braking, and fault detection, enhancing the overall performance and reliability of the system.

The integration of timing circuits within the control logic is essential for minimizing EMI, which can adversely affect nearby electronic devices. The use of a Schmitt trigger inverter for the rising edge ensures a clean transition, reducing the risk of false triggering due to noise. The fast discharge capability of the open collector inverter on the falling edge contributes to rapid turn-off times, minimizing the duration of high current spikes that can lead to EMI.

The choice of timing components, such as the capacitors and resistors, directly influences the delay characteristics of the circuit. The values selected (10KΩ with 0.1µF and 10Ω with 3.9µF) provide a balance between responsiveness and stability, allowing for fine-tuning of the delays to optimize performance. The design must also consider thermal management, as the high-current operation of the H-bridge drivers generates heat, which must be dissipated effectively to prevent component failure.

In conclusion, the proposed design revision not only addresses the immediate concerns of current spikes and EMI but also enhances the overall functionality and adaptability of the H-bridge driver circuit. By leveraging modern microprocessor or CPLD technology, the design can evolve to meet future requirements while maintaining robust performance in demanding applications.The following is an account of such an undertaking. Recently I was involved in a design review for a cost reduction project, where an older design was getting an update. The new design was a merging of two different designs, including someupdated parts and some existing controls.

The design includes six 10Amp H-bridge drivers and the associated control logic. Some of the early testing had shown some rather large current spikes and also some higher than desirable amounts of electromagnetic interference (EMI). A consultant who had been helping out on a similar design, mostly on EMI concerns, had suggested a few timing changes to the circuitry.

As the talks continued, two different schemes involving changes to the timing were discussed. At this point, I had jumped in and suggested that we pull out all the control circuitry and replace it with a small microprocessor or a CPLD, allowing us some freedom to make changes in the timing schemes. My manager had referred to my suggestion as "a small joke", but I assured him I was serious. A couple of days later I met with my manager and we talked a little more about the idea of handling the bridge control logic inside of a small microprocessor.

After we are able to agree that it would in fact be possible (and also a good idea to do so), we quickly defined the desired level of control and the range of the different delays that we would need to consider. Great, we have a plan and a direction. Before we jump into the work, let`s take a moment and analyze the current circuit to determine present functionality and the actual delay times in order to better understand our starting point.

The big picture view on the circuit is actually quite simple. Changes in the `Direction` line require proper sequencing of the current source and the bridge drivers. On a change in direction, the presently selected drivers (opposite side, top and bottom MOSFETs) are disabled along with the programmable current source.

Then a delay occurs before enabling the opposite set of MOSFETs, along with another delay prior to re-enabling the current source. It is the sequence of these actions and the time delays that will have effects on the operation and resulting EMI characteristics of our six H-bridges.

In the above schematic there are two different delay circuits (two copies using 10K and 0. 1uF, plus one using 10 and 3. 9uF). The direction control circuits each use two different inverters (an open collector type - SN7406 and a Schmitt trigger type - 74HTC14). Each of these inverters are use to control a different edge of the transitions, the Schmitt trigger controls the rising edge (enable), by applying a charging current through a series resistor into a timing capacitor (0.

1uF) to cause a fixed delay, while the open collector inverter controls the falling edge (disable), by using a high current dump of the charge on the capacitor to effect a near zero delay turn off. The combination of the two inverter types is actually a clever approach. The Schmitt trigger device drives both high and low at ~4ma, while the Open Collector device provides no drive in high, but can sink ~40ma during the low state, providing controlled rise time and fast fall time.

The second delay circuit is used to control the programmable current source by temporarily disabling the current source during the direction changes. This stage uses a single Open Collecto 🔗 External reference