digital counter circuits

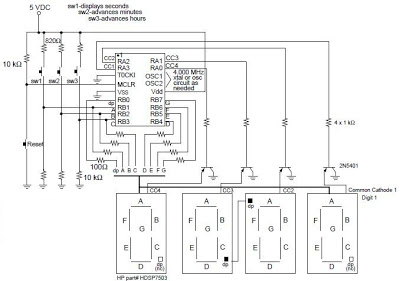

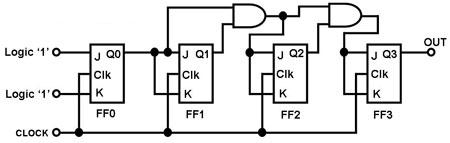

The circuit in Figure 1 is a 4-bit asynchronous counter, also known as a ripple counter. It consists of four J-K flip-flops with their J and K inputs connected to logic 1. This configuration causes the output of each J-K flip-flop to toggle with each clock pulse. By utilizing the output of the preceding flip-flop to clock the next one, a rippling effect is achieved, allowing the flip-flops to count in binary. The circuit in Figure 2 is a 4-bit synchronous counter, which also comprises four J-K flip-flops, but all are clocked simultaneously, hence the term synchronous counter. The toggling of the outputs of the flip-flops in this counter is contingent upon the states of their J and K inputs. It is important to note that the output of a J-K flip-flop will only toggle when both J and K are high. The first flip-flop (least significant bit) in a synchronous counter has its J and K inputs directly connected to logic 1, enabling its output to toggle automatically with each clock pulse. The J and K inputs of the second flip-flop are connected to the output of the first flip-flop, meaning that it will toggle at half the rate of the first flip-flop, even with simultaneous clocking. The J and K inputs of the subsequent flip-flops are connected to an AND gate, which receives inputs from the outputs of the two preceding flip-flops. This design ensures that each of these flip-flops toggles at half the frequency of the flip-flop before it, despite being clocked simultaneously.

The 4-bit asynchronous counter, or ripple counter, operates on the principle of sequential toggling of J-K flip-flops. In this configuration, the first flip-flop toggles its output state with each incoming clock pulse due to its J and K inputs being held high. This output then serves as the clock input for the next flip-flop, creating a cascading effect. Each subsequent flip-flop toggles based on the output of the previous one, resulting in a binary count that propagates through the flip-flops, hence the term "ripple." The counter counts up from 0 to 15 in binary (0000 to 1111) before resetting back to 0.

In contrast, the 4-bit synchronous counter achieves its counting mechanism through simultaneous clocking of all flip-flops. The first flip-flop still has its J and K inputs tied to logic 1, allowing it to toggle with each clock pulse. However, the second flip-flop's inputs are derived from the output of the first flip-flop, leading to a toggle rate that is half that of the first flip-flop. This pattern continues with each subsequent flip-flop being controlled by an AND gate that combines the outputs of the two preceding flip-flops, ensuring that the toggling continues at a halved rate, thus maintaining the binary counting sequence.

This synchronous design minimizes the propagation delay issues associated with asynchronous counters, making it more suitable for applications requiring precise timing and synchronization. The overall architecture of both counters illustrates fundamental principles of digital electronics, particularly in the use of flip-flops for counting and state storage.The circuit in Figure 1 is that of a 4-bit asynchronous counter, also known as a `ripple counter`. It consists of 4 J-K flip-flops whose J and K inputs are tied to logic `1`. This connection causes the output of each J-K flip-flop to toggle every time it gets a clock pulse. By using the output of the previous flip-flop to clock the next flip-flop, a `rippling` effect is achieved causing the flip-flops to count in binary fashion. The circuit in Figure 2 is that of a 4-bit synchronous counter. It consists of 4 J-K flip-flops, all of which are clocked at the same time, hence the name `synchronous counter`. Thus, the toggling of the output of the flip-flops in this counter depends on the states of their J and K inputs.

Recall that the J-K flip-flop`s output will only toggle when both J and K are `high`. The first flip-flop (lease-significant bit) of a synchronous counter has its J and K inputs directly tied to logic `1`. This causes its output to toggle automatically every time it gets a clock pulse. The second flip-flop`s J and K inputs are directly tied to the output of the first flip-flop. Thus, even if they get clocked at the same time, the second flip-flop will only toggle half the times as the first one.

The subsequent flip-flops` J and K inputs are tied to an AND gate whose inputs are tied to the outputs of the last two flip-flops before it. This ensures that each of these flip-flops will toggle at half the rate as the flip-flop before it, even if they are all clocked at the same time.

🔗 External reference

The 4-bit asynchronous counter, or ripple counter, operates on the principle of sequential toggling of J-K flip-flops. In this configuration, the first flip-flop toggles its output state with each incoming clock pulse due to its J and K inputs being held high. This output then serves as the clock input for the next flip-flop, creating a cascading effect. Each subsequent flip-flop toggles based on the output of the previous one, resulting in a binary count that propagates through the flip-flops, hence the term "ripple." The counter counts up from 0 to 15 in binary (0000 to 1111) before resetting back to 0.

In contrast, the 4-bit synchronous counter achieves its counting mechanism through simultaneous clocking of all flip-flops. The first flip-flop still has its J and K inputs tied to logic 1, allowing it to toggle with each clock pulse. However, the second flip-flop's inputs are derived from the output of the first flip-flop, leading to a toggle rate that is half that of the first flip-flop. This pattern continues with each subsequent flip-flop being controlled by an AND gate that combines the outputs of the two preceding flip-flops, ensuring that the toggling continues at a halved rate, thus maintaining the binary counting sequence.

This synchronous design minimizes the propagation delay issues associated with asynchronous counters, making it more suitable for applications requiring precise timing and synchronization. The overall architecture of both counters illustrates fundamental principles of digital electronics, particularly in the use of flip-flops for counting and state storage.The circuit in Figure 1 is that of a 4-bit asynchronous counter, also known as a `ripple counter`. It consists of 4 J-K flip-flops whose J and K inputs are tied to logic `1`. This connection causes the output of each J-K flip-flop to toggle every time it gets a clock pulse. By using the output of the previous flip-flop to clock the next flip-flop, a `rippling` effect is achieved causing the flip-flops to count in binary fashion. The circuit in Figure 2 is that of a 4-bit synchronous counter. It consists of 4 J-K flip-flops, all of which are clocked at the same time, hence the name `synchronous counter`. Thus, the toggling of the output of the flip-flops in this counter depends on the states of their J and K inputs.

Recall that the J-K flip-flop`s output will only toggle when both J and K are `high`. The first flip-flop (lease-significant bit) of a synchronous counter has its J and K inputs directly tied to logic `1`. This causes its output to toggle automatically every time it gets a clock pulse. The second flip-flop`s J and K inputs are directly tied to the output of the first flip-flop. Thus, even if they get clocked at the same time, the second flip-flop will only toggle half the times as the first one.

The subsequent flip-flops` J and K inputs are tied to an AND gate whose inputs are tied to the outputs of the last two flip-flops before it. This ensures that each of these flip-flops will toggle at half the rate as the flip-flop before it, even if they are all clocked at the same time.

🔗 External reference