Digital Fan Regulator Circuit PCB

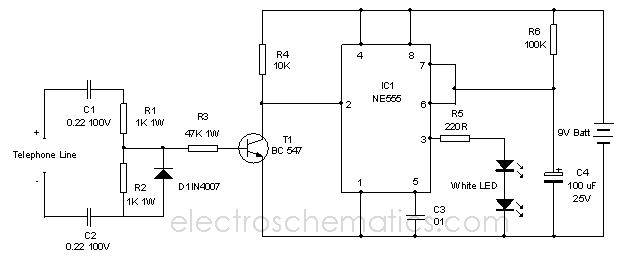

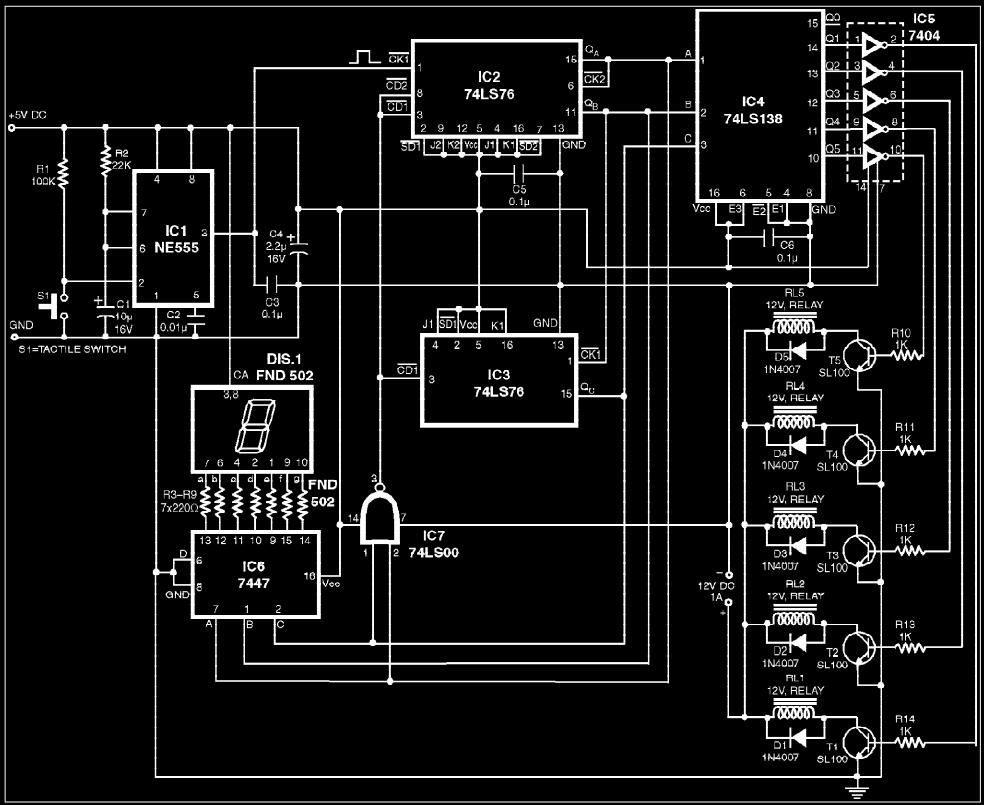

The circuit presented is a digital fan regulator that offers five speed levels, similar to conventional fan regulators. This ceiling fan controller utilizes readily available components. An optional 7-segment display with associated circuitry is included to show the selected fan speed. The core of the circuit is a modulo-6 binary counter, constructed using IC2 and IC3 (IC 7476), which are dual JK flip-flops. The counter increments in binary from 000 to 101 (0 to 5) with each clock edge and resets to 000 after reaching the maximum count. Each flip-flop toggles on the falling edge of the clock. Assuming the counter starts at 000 when powered on, a monostable multivibrator built around IC1 (NE 555) generates necessary pulses to trigger the counter with each press of switch S1. Upon the first clock edge, the counter moves to 001. The counter outputs connect to IC4 (IC 74138), a 3-line to 8-line decoder. When IC4 receives the input address 001, its output Q1 goes low while other outputs remain high. The inverted output Q1 drives transistor T1, activating relay RL1, which supplies power to the fan via the normally open contact RL1/1 and a tapped resistor RT. This tapped resistor can be a conventional resistance found in standard fan regulators. The counter outputs also connect to IC6 (IC 7447), a BCD to 7-segment code converter, which drives a 7-segment LED display. When switch S1 is pressed again, the counter advances to 010, causing output Q2 of IC4 to go low while other outputs remain high. This action saturates transistor T2 and activates relay RL2, with the display reflecting the current counter output. The counter continues to increment with each press of switch S1 until reaching 101. Upon the next press, the counter would typically read 110; however, the two most significant bits force the output of NAND gate (IC7) to go low, resetting the counter back to 000. The counting sequence then restarts with each subsequent key press.

The digital fan regulator circuit effectively manages fan speed through a straightforward user interface and reliable component selection. The use of dual JK flip-flops allows for precise counting and toggling behavior, essential for maintaining the desired speed levels. The NE 555 timer, configured as a monostable multivibrator, ensures that each press of the switch generates a clean pulse, preventing erroneous counts due to switch bounce. The 3-line to 8-line decoder (IC74138) efficiently translates the binary count into control signals for the relays, enabling smooth transitions between speed settings.

The relays, controlled by the transistors, provide isolation between the low-voltage control circuitry and the high-voltage fan circuit, ensuring safety and reliability. The tapped resistor RT is critical for adjusting the fan speed and can be tailored based on the fan's specifications, allowing for a customizable user experience. The integration of a 7-segment display enhances usability by providing real-time feedback on the current speed setting, making it easier for users to select their preferred speed.

Overall, this digital fan regulator circuit exemplifies a practical application of digital electronics in everyday appliances, combining functionality with user-friendly features. The design is scalable and can be modified to accommodate additional features, such as remote control capabilities or integration with smart home systems, further enhancing its versatility and appeal.The circuit presented here is that of a digital fan regulator, variable to provide five speed levels as catered for in ordinary fan regulators. The circuit of ceiling fan controller makes use of easily available components. An optional 7-segment display with its associated electronic circuitry has been provided to display your choice of fan speed.

The heart of the circuit is a modulo-6 binary counter, built around IC2 and IC3 (IC 7476) which are dual JK flip-flops. The counter counts up in a straight binary progression from 000 to 101 (i. e. from 0 to 5) upon each successive clock edge and is reset to 000 upon next clock. The count sequence of the counter has been summarized in Table I. Each flip-flop is configured to toggle when the clock goes from high to low. Let us begin with the assumption that the counter reads 000 at power on. The monoshot built around IC1 (NE 555) provides necessary pulses to trigger the counter upon every depression of switch S1.

Upon the arrival of first clock edge, the counter advances to 001. The outputs of the counter go to IC4 (IC 74138), which is a 3-line to 8-line decoder. When IC4 receives the input address 001, its output Q1 goes low, while other outputs Q0 and Q2 through Q7 stay high. The output Q1, after inversion, drives transistor T1, which actuates relay RL1. Now power is delivered to the fan through the N/O contact RL1/1 of relay RL1 and the tapped resistor RT.

For the tapped resistor RT, one can use the resistance found in conventional fan regulators with rotary speed regulation. The outputs of the counter also go to IC6 (IC 7447), a BCD to 7-segment code converter, which, in turn, drives a 7-segment LED display.

When switch S1 is depressed once again, the counter advances to count 010. Now, the output Q2 of IC4 goes low, while Q0, Q1 and Q3 through Q7 go high or remain high. This forces transistor T2 to saturation and actuates relay RL2. The display indicates the counter output in a 7-segment fashion. The counter proceeds through its normal count sequence upon every depression of switch S1 up to the count 101. When switch S1 is depressed once again, normally the counter should read 110. But the two most significant bits of the counter force the output of NAND gate (IC7) to go low to reset the counter to 000.

The counter now begins to count through its normal sequence all over again, upon every key depression. 🔗 External reference

The digital fan regulator circuit effectively manages fan speed through a straightforward user interface and reliable component selection. The use of dual JK flip-flops allows for precise counting and toggling behavior, essential for maintaining the desired speed levels. The NE 555 timer, configured as a monostable multivibrator, ensures that each press of the switch generates a clean pulse, preventing erroneous counts due to switch bounce. The 3-line to 8-line decoder (IC74138) efficiently translates the binary count into control signals for the relays, enabling smooth transitions between speed settings.

The relays, controlled by the transistors, provide isolation between the low-voltage control circuitry and the high-voltage fan circuit, ensuring safety and reliability. The tapped resistor RT is critical for adjusting the fan speed and can be tailored based on the fan's specifications, allowing for a customizable user experience. The integration of a 7-segment display enhances usability by providing real-time feedback on the current speed setting, making it easier for users to select their preferred speed.

Overall, this digital fan regulator circuit exemplifies a practical application of digital electronics in everyday appliances, combining functionality with user-friendly features. The design is scalable and can be modified to accommodate additional features, such as remote control capabilities or integration with smart home systems, further enhancing its versatility and appeal.The circuit presented here is that of a digital fan regulator, variable to provide five speed levels as catered for in ordinary fan regulators. The circuit of ceiling fan controller makes use of easily available components. An optional 7-segment display with its associated electronic circuitry has been provided to display your choice of fan speed.

The heart of the circuit is a modulo-6 binary counter, built around IC2 and IC3 (IC 7476) which are dual JK flip-flops. The counter counts up in a straight binary progression from 000 to 101 (i. e. from 0 to 5) upon each successive clock edge and is reset to 000 upon next clock. The count sequence of the counter has been summarized in Table I. Each flip-flop is configured to toggle when the clock goes from high to low. Let us begin with the assumption that the counter reads 000 at power on. The monoshot built around IC1 (NE 555) provides necessary pulses to trigger the counter upon every depression of switch S1.

Upon the arrival of first clock edge, the counter advances to 001. The outputs of the counter go to IC4 (IC 74138), which is a 3-line to 8-line decoder. When IC4 receives the input address 001, its output Q1 goes low, while other outputs Q0 and Q2 through Q7 stay high. The output Q1, after inversion, drives transistor T1, which actuates relay RL1. Now power is delivered to the fan through the N/O contact RL1/1 of relay RL1 and the tapped resistor RT.

For the tapped resistor RT, one can use the resistance found in conventional fan regulators with rotary speed regulation. The outputs of the counter also go to IC6 (IC 7447), a BCD to 7-segment code converter, which, in turn, drives a 7-segment LED display.

When switch S1 is depressed once again, the counter advances to count 010. Now, the output Q2 of IC4 goes low, while Q0, Q1 and Q3 through Q7 go high or remain high. This forces transistor T2 to saturation and actuates relay RL2. The display indicates the counter output in a 7-segment fashion. The counter proceeds through its normal count sequence upon every depression of switch S1 up to the count 101. When switch S1 is depressed once again, normally the counter should read 110. But the two most significant bits of the counter force the output of NAND gate (IC7) to go low to reset the counter to 000.

The counter now begins to count through its normal sequence all over again, upon every key depression. 🔗 External reference