DIVIDE BY ODD NUMBER COUNTER

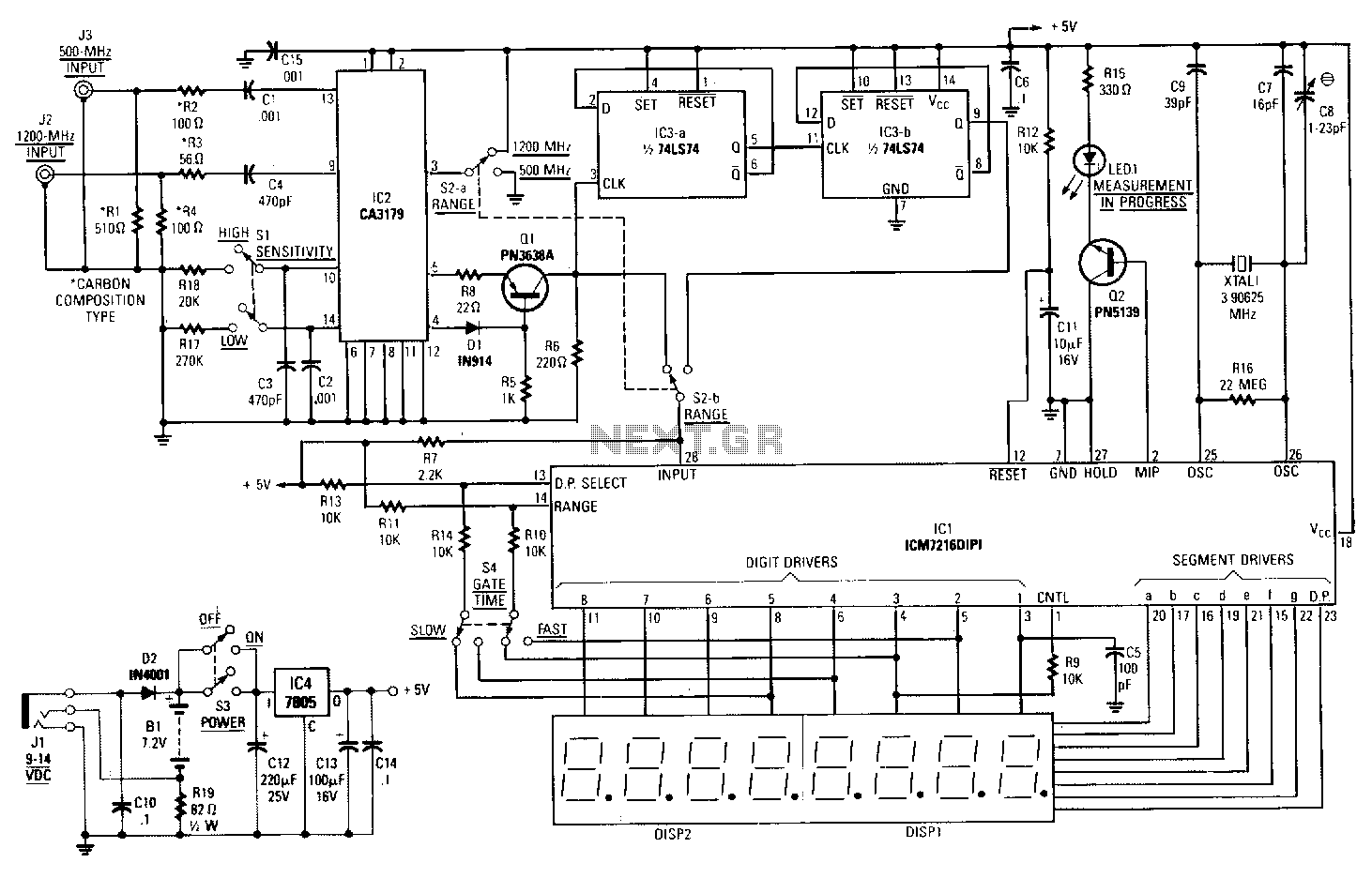

This circuit symmetrically divides an input by virtually any odd number. The circuit contains n+l/2 clocks twice to achieve the desired divisor. By selecting the proper n, which is the decoded output of the 74LS161 counter, divisors from 3 to 31 can be obtained. This circuit specifically divides by 25; higher divisors can be achieved by cascading additional LS161 counters. The counter and IC5A form the n+l/2 counter. Once the counter reaches the decoded counts, n, IC5A ticks off an additional 1/2 clock, which clears the counter and puts it in hold. Additionally, IC5A clocks IC5B, which changes the clock phasing through the XOR gate, IC1. The next edge of the input clocks IC5A, which re-enables the counter to start counting for an additional n+l/2 cycles.

The circuit is designed to symmetrically divide an input signal by any specified odd number, utilizing a combination of clock cycles and counters. The heart of the circuit is based on the 74LS161 binary counter, which allows for the selection of divisors ranging from 3 to 31, depending on the value of n, which is determined by the counter's decoded output. The architecture incorporates an n+l/2 clocking mechanism, effectively doubling the clock input to achieve the required division.

The operation begins when the 74LS161 counter counts up to the specified value n. Upon reaching this count, an additional half clock pulse is generated by IC5A, which serves to clear the counter and place it in a hold state, thus preventing further counting until the next cycle. This mechanism ensures that the circuit can maintain stability and accuracy in its output.

Additionally, IC5A plays a pivotal role in clocking IC5B, modifying the clock phasing through the XOR gate (IC1). This adjustment is crucial as it alters the timing of the subsequent clock edges, allowing for precise control over the counting sequence. When the input clock signal edges, IC5A is re-enabled, prompting the counter to resume counting for another n+l/2 cycles. This cyclical process allows for the generation of higher divisors by cascading multiple 74LS161 counters, thereby expanding the circuit's capability to divide by larger odd numbers beyond the initial configuration.

Overall, this circuit design provides a robust solution for generating odd divisors through an efficient combination of counter logic and clock manipulation, making it suitable for various applications in digital electronics where precise frequency division is required.This circuit symmetrically divides an input by virtually any odd number. The circuit contains n+l/2 clocks twice to achieve the desired divisor. By selecting the proper n, which is the decoded output of the 74LS161 counter, you can obtain diisors from 3 to 31. This circuit divides by 25; you can obtain higher divisors by cascading additional LS161

🔗 External reference

The circuit is designed to symmetrically divide an input signal by any specified odd number, utilizing a combination of clock cycles and counters. The heart of the circuit is based on the 74LS161 binary counter, which allows for the selection of divisors ranging from 3 to 31, depending on the value of n, which is determined by the counter's decoded output. The architecture incorporates an n+l/2 clocking mechanism, effectively doubling the clock input to achieve the required division.

The operation begins when the 74LS161 counter counts up to the specified value n. Upon reaching this count, an additional half clock pulse is generated by IC5A, which serves to clear the counter and place it in a hold state, thus preventing further counting until the next cycle. This mechanism ensures that the circuit can maintain stability and accuracy in its output.

Additionally, IC5A plays a pivotal role in clocking IC5B, modifying the clock phasing through the XOR gate (IC1). This adjustment is crucial as it alters the timing of the subsequent clock edges, allowing for precise control over the counting sequence. When the input clock signal edges, IC5A is re-enabled, prompting the counter to resume counting for another n+l/2 cycles. This cyclical process allows for the generation of higher divisors by cascading multiple 74LS161 counters, thereby expanding the circuit's capability to divide by larger odd numbers beyond the initial configuration.

Overall, this circuit design provides a robust solution for generating odd divisors through an efficient combination of counter logic and clock manipulation, making it suitable for various applications in digital electronics where precise frequency division is required.This circuit symmetrically divides an input by virtually any odd number. The circuit contains n+l/2 clocks twice to achieve the desired divisor. By selecting the proper n, which is the decoded output of the 74LS161 counter, you can obtain diisors from 3 to 31. This circuit divides by 25; you can obtain higher divisors by cascading additional LS161

counters. The counter and IC5A form the n+l/2 counter. Once the counter reaches the decoded counts, n, IC5A ticks off an additional 1/2 clock, which clears the counter and puts it in hold. Additionally, IC5A clocks IC5B, which changes the dock phasing through the X0R gate, IC1. The next edge of the input clocks IC5A, which reenables the counter to start counting for an additional n+l/2 cycles.

🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713