ESD Testing for RS232 Interface Circuits

The machine model ESD testing is an essential procedure for evaluating the robustness of electronic devices against electrostatic discharge (ESD). In this testing configuration, a charged body contacts the device under test (DUT), simulating a worst-case scenario for ESD susceptibility. The use of a 200pF capacitor without a limiting resistor subjects the DUT to significant voltage and current spikes, leading to potential failure at lower thresholds compared to the human body model testing, which utilizes a more forgiving approach.

LTC’s RS232 transceivers exhibit a remarkable resilience to ESD, withstanding voltage levels of ±3.5kV under the machine model tests. The IEC-801 standard offers a middle ground in terms of severity, employing a 150pF capacitor along with a 330Ω limiting resistor, allowing the RS232 transceivers to endure test voltages of ±7.5kV. This highlights the importance of selecting appropriate test methodologies based on the expected operational environment and potential ESD threats.

Furthermore, the ability of LTC’s RS232 interface circuits to tolerate ESD transients up to 10kV during powered operation is critical for portable electronics, where connections to communication ports may occur while the device is operational. Although ESD transients can cause temporary disruptions in data transmission, the circuits are designed to recover within approximately 20µs post-incident. This rapid recovery is crucial for maintaining system integrity and ensuring minimal downtime.

The described testing methodology and results underscore the importance of robust design practices in electronic circuit development, particularly in environments susceptible to ESD events. The outlined testing scenarios, including the application of ESD strikes to specific components like the LT1180A driver and LT1331 receiver, provide valuable insights into the transient behavior of these circuits and their ability to recover from disruptive events effectively.The machine model, commonly used for ESD testing in Japan, is a more severe ESD test. This model simulates metallic contact between the device under test and a charged body. The source capacitor is 200pF with no limiting resistor. The higher source capacitance and the absence of a limiting resistor causes the device under test to be subjected to more voltage, energy, and current than human body model testing. Therefore failures occur at lower test voltages with machine model than with human body model testing.

LTC’s RS232 transceivers can withstand ±3.5kV when tested with the machine model. The IEC-801 test method fi ts between the human body and machine methods in severity. The source capacitor is 150pF with a 330Ω limiting resistor. LTC’s RS232 transceivers pass test voltages of ±7.5kV with the IEC-801 method.

ESD Transients During Powered Operation The test methods discussed so far involve testing for permanent damage to the integrated circuit from ESD transients. In today’s portable electronics, interconnection of cables to the communications ports may occur while the equipment is operating.

This makes it imperative that the circuit can tolerate the ESD transient with minimal disruption of system operation. LTC’s RS232 interface circuits can withstand 10kV ESD transients while operating, shut down, or powered down.

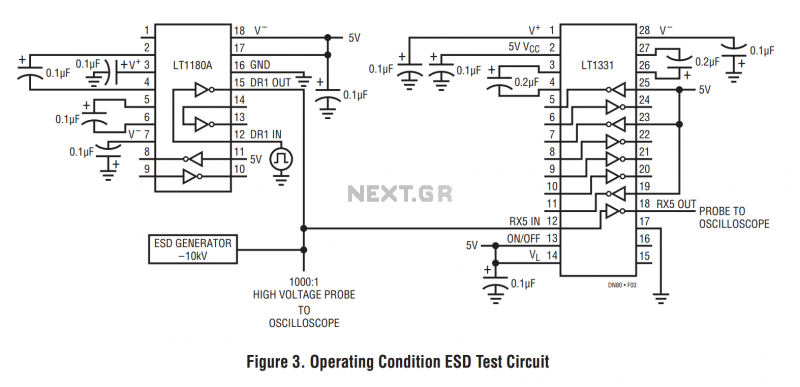

Disruption of data transfer is unavoidable during the ESD transient event, but data transmission may resume upon the completion of the event. Figure 2 is a scope photograph of the data transmission interruption and recovery seen when a –10kV ESD transient strikes a communications line.

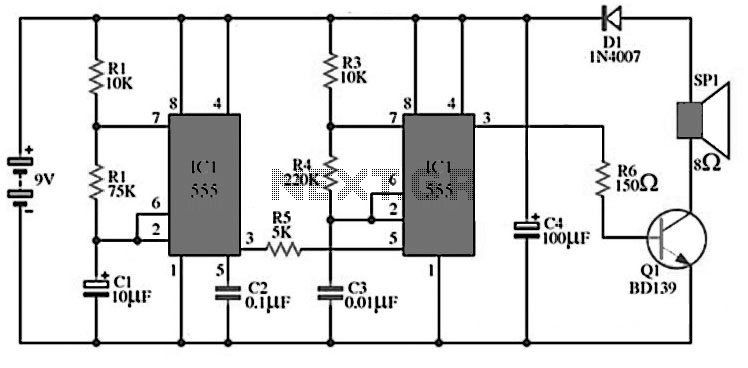

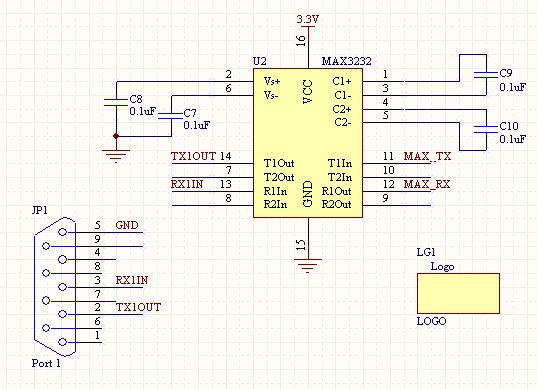

The test circuit of Figure 3 was used to record this event. The ESD strike is applied to the driver output of an LT1180A and the receiver input of an LT1331. The ESD transient is of too short a duration to be recorded on the photograph, but the effects of the transient can be seen by the corruption of data after the strike. The circuits require about 20μs to recover from the event, after which data transmission continues normally

🔗 External reference