Fast Pulse Detector

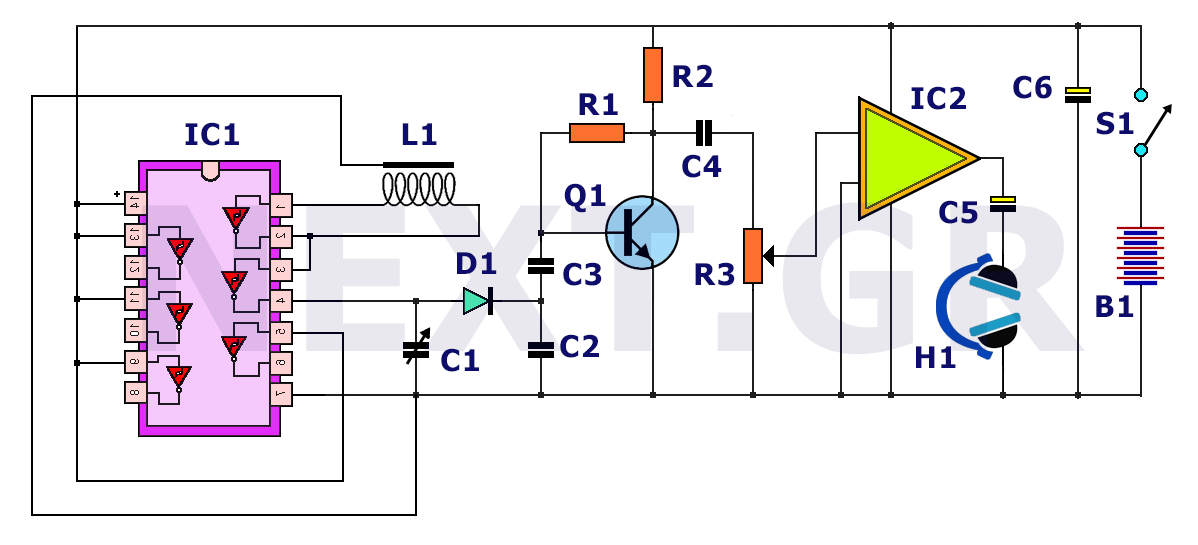

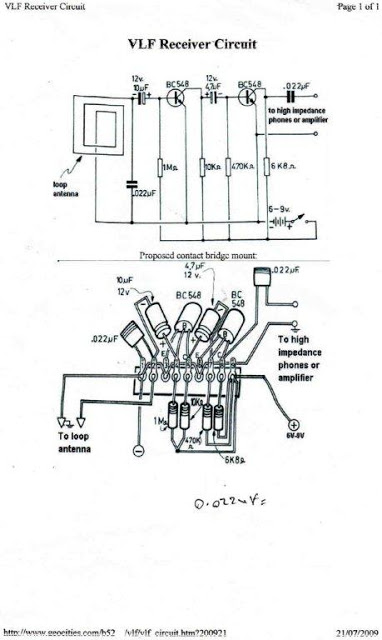

A schematic diagram of a fast pulse detector is shown in the figure below. An error detection rate of under 10% can be expected for a 60 ns pulse to achieve error-free operation.

The fast pulse detector circuit is designed to accurately identify and process rapid pulse signals, making it suitable for applications in digital communications, radar systems, and high-speed data acquisition systems. The key components of the schematic typically include a high-speed comparator, a pulse shaping circuit, and a signal conditioning stage.

The high-speed comparator is essential for detecting the presence of the pulse. It compares the incoming signal against a predefined threshold level. When the signal exceeds this threshold, the comparator outputs a logic high signal, indicating the detection of a pulse. The choice of comparator is critical, as it must have a fast response time to handle the 60 ns pulse width effectively.

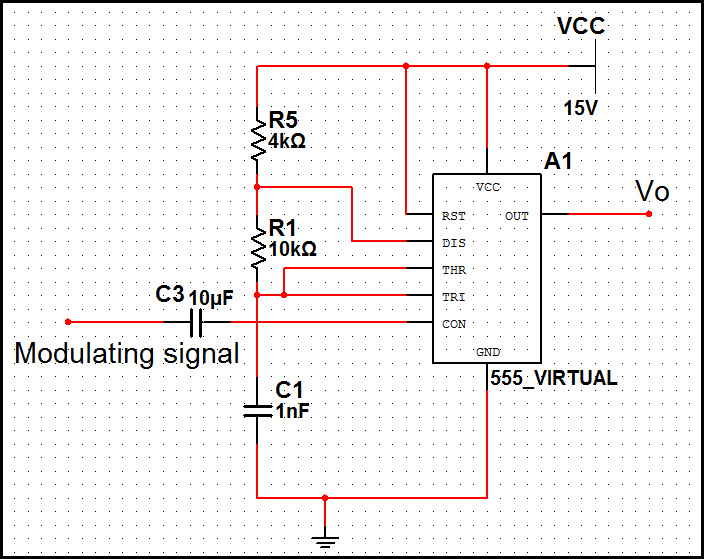

Following the comparator, the pulse shaping circuit refines the detected signal to ensure that it has a clean rise and fall time, which is crucial for subsequent processing stages. This may involve the use of resistors and capacitors to form an RC network that filters out noise and reduces ringing.

The signal conditioning stage may include additional filtering, amplification, and level shifting to prepare the signal for further processing or interfacing with digital logic circuits. This stage ensures that the output signal maintains integrity and is compatible with the input requirements of downstream components.

Overall, the design of the fast pulse detector circuit emphasizes speed and accuracy, achieving an error detection rate of less than 10% for 60 ns pulses, thus facilitating reliable operation in high-speed applications. Proper layout and component selection are vital to minimize propagation delays and ensure the circuit's performance meets the specified criteria.A schematic diagram of a fast pulse detector is show in the figure below. Error detection rate under 10% can be expected for 60 ns pulse. To get error free.. 🔗 External reference

The fast pulse detector circuit is designed to accurately identify and process rapid pulse signals, making it suitable for applications in digital communications, radar systems, and high-speed data acquisition systems. The key components of the schematic typically include a high-speed comparator, a pulse shaping circuit, and a signal conditioning stage.

The high-speed comparator is essential for detecting the presence of the pulse. It compares the incoming signal against a predefined threshold level. When the signal exceeds this threshold, the comparator outputs a logic high signal, indicating the detection of a pulse. The choice of comparator is critical, as it must have a fast response time to handle the 60 ns pulse width effectively.

Following the comparator, the pulse shaping circuit refines the detected signal to ensure that it has a clean rise and fall time, which is crucial for subsequent processing stages. This may involve the use of resistors and capacitors to form an RC network that filters out noise and reduces ringing.

The signal conditioning stage may include additional filtering, amplification, and level shifting to prepare the signal for further processing or interfacing with digital logic circuits. This stage ensures that the output signal maintains integrity and is compatible with the input requirements of downstream components.

Overall, the design of the fast pulse detector circuit emphasizes speed and accuracy, achieving an error detection rate of less than 10% for 60 ns pulses, thus facilitating reliable operation in high-speed applications. Proper layout and component selection are vital to minimize propagation delays and ensure the circuit's performance meets the specified criteria.A schematic diagram of a fast pulse detector is show in the figure below. Error detection rate under 10% can be expected for 60 ns pulse. To get error free.. 🔗 External reference

.png)