Fast Pulse Detector Circuit

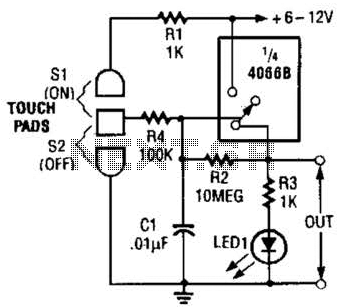

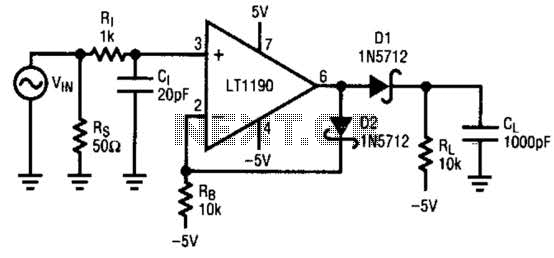

A fast pulse detector can be constructed using this circuit. A very fast input pulse will surpass the amplifier's slew rate, resulting in a prolonged overload recovery time. Implementing some degree of dv/dt limiting on the input can alleviate this overload condition; however, it may introduce a delay in the response.

A fast pulse detector circuit is designed to identify rapid changes in input signals, particularly those that may exceed the operational limits of the amplifier used within the circuit. The primary challenge arises when the input pulse's rate of change, denoted as dv/dt, exceeds the amplifier's slew rate. This condition can lead to distortion and a significant delay in the recovery time of the amplifier, preventing accurate pulse detection.

To mitigate the effects of exceeding the slew rate, dv/dt limiting techniques can be applied to the input signal. This can be achieved through the integration of passive components such as resistors and capacitors that form a low-pass filter, effectively smoothing out the rapid transitions of the input pulse. While this approach helps to prevent overload conditions, it is important to note that the filtering process may introduce a delay in the circuit's response time.

In a typical fast pulse detector circuit, the configuration may include an operational amplifier (op-amp) set up in a non-inverting configuration, allowing for the amplification of the input signal. The feedback network should be designed to maintain stability while accommodating the required slew rate. Additionally, the input stage may incorporate a diode clamping mechanism to protect the op-amp from excessive voltage levels caused by fast transients.

The output of the pulse detector can be connected to subsequent digital logic circuits or microcontrollers for further processing. It is crucial to ensure that the output stage is capable of driving the intended load without distortion, maintaining the integrity of the detected pulse.

In summary, while a fast pulse detector circuit can effectively identify rapid input signals, careful consideration must be given to the amplifier's slew rate and the implementation of dv/dt limiting to ensure reliable operation without significant delays in response time. A fast pulse detector can be made with this circuit. A very fast input pulse will exceed the amplifier slew rate and cause a long overload recovery time. Some amount of dv/dt limiting on the input can help This overload condition, however this will delay the response. 🔗 External reference

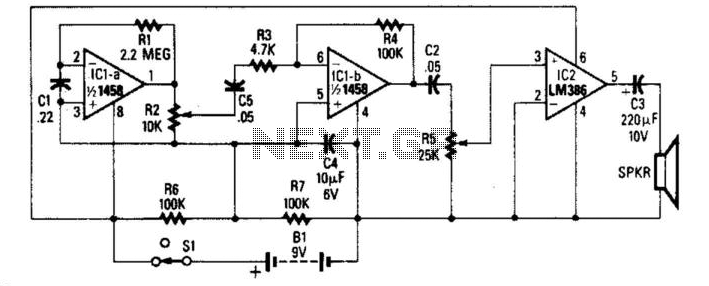

A fast pulse detector circuit is designed to identify rapid changes in input signals, particularly those that may exceed the operational limits of the amplifier used within the circuit. The primary challenge arises when the input pulse's rate of change, denoted as dv/dt, exceeds the amplifier's slew rate. This condition can lead to distortion and a significant delay in the recovery time of the amplifier, preventing accurate pulse detection.

To mitigate the effects of exceeding the slew rate, dv/dt limiting techniques can be applied to the input signal. This can be achieved through the integration of passive components such as resistors and capacitors that form a low-pass filter, effectively smoothing out the rapid transitions of the input pulse. While this approach helps to prevent overload conditions, it is important to note that the filtering process may introduce a delay in the circuit's response time.

In a typical fast pulse detector circuit, the configuration may include an operational amplifier (op-amp) set up in a non-inverting configuration, allowing for the amplification of the input signal. The feedback network should be designed to maintain stability while accommodating the required slew rate. Additionally, the input stage may incorporate a diode clamping mechanism to protect the op-amp from excessive voltage levels caused by fast transients.

The output of the pulse detector can be connected to subsequent digital logic circuits or microcontrollers for further processing. It is crucial to ensure that the output stage is capable of driving the intended load without distortion, maintaining the integrity of the detected pulse.

In summary, while a fast pulse detector circuit can effectively identify rapid input signals, careful consideration must be given to the amplifier's slew rate and the implementation of dv/dt limiting to ensure reliable operation without significant delays in response time. A fast pulse detector can be made with this circuit. A very fast input pulse will exceed the amplifier slew rate and cause a long overload recovery time. Some amount of dv/dt limiting on the input can help This overload condition, however this will delay the response. 🔗 External reference