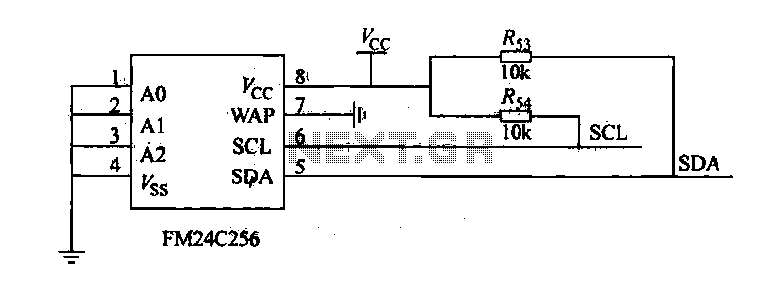

FM24C256 interface circuit

The FM24C256 is utilized as a slave interface circuit in an I2C bus configuration, with the address format specified in Table 27-3. The address pins A2, A1, and A0 are set to low; however, for extended storage capacity, adjustments to these pins are necessary. The lowest address is used to write the control bit, where '1' indicates a read operation from the device, while '0' signifies a slave write operation. A start signal is initiated by the controller MCU, followed by the device address byte. The FM24C256 monitors the bus and responds when its address matches the transmitted address, executing the appropriate read or write operation based on the state of the read/write control pin (R/W). The MM36SB020 chip is designed for storing 16x16 dot matrix Chinese characters, with control commands detailed in the MM36SB020 documentation.

The FM24C256 is a 256 Kbit non-volatile memory device that interfaces with microcontrollers via the I2C communication protocol. In this application, it operates as a slave device, responding to commands from a master device, typically a microcontroller. The configuration of the address pins (A2, A1, A0) determines the device's address on the I2C bus, allowing for multiple devices to coexist on the same bus by assigning them unique addresses.

When the microcontroller initiates communication, it sends a start condition followed by the address byte, which includes the read/write bit. If the read/write bit is set to '1', the FM24C256 prepares to send data to the master device. Conversely, if the bit is '0', the master device is writing data to the FM24C256. The control bit at the lowest address allows the microcontroller to specify the operation type, ensuring that the correct action is taken based on the intended operation.

The MM36SB020 chip complements the FM24C256 by providing storage for Chinese characters in a 16x16 dot matrix format. It is essential for applications that require the display of Chinese characters on screens or other output devices. The control commands for the MM36SB020 are crucial for managing how characters are stored, retrieved, and displayed, allowing for efficient rendering of text in applications where Chinese language support is necessary.

Overall, this configuration illustrates a typical use case of I2C communication for memory management and character display, showcasing the integration of different components to achieve a specific functionality in electronic systems.FM24C256 as shown 27-54 slave interface circuit I2C bus, the address format shown in Table 27-3. A2, Al, AO is set to low (when extended storage capacity, the need to change A2 , A1, AO setting), the lowest address to write control bit, which is. 1 expressed a read operation from the device as a o indicates to be a slave write operation start signal is sent from the controller MCU and after the device address byte. FM24C256 monitors the bus, when its address is sent from the device to match the address when, in response to a signal should blame; perform the appropriate read/write operation according to the state read and write control Pina bit R/Ws.

MM36SB020 chip for storing 16 16 dot matrix Chinese character. Control commands are shown in Table MM36SB020

The FM24C256 is a 256 Kbit non-volatile memory device that interfaces with microcontrollers via the I2C communication protocol. In this application, it operates as a slave device, responding to commands from a master device, typically a microcontroller. The configuration of the address pins (A2, A1, A0) determines the device's address on the I2C bus, allowing for multiple devices to coexist on the same bus by assigning them unique addresses.

When the microcontroller initiates communication, it sends a start condition followed by the address byte, which includes the read/write bit. If the read/write bit is set to '1', the FM24C256 prepares to send data to the master device. Conversely, if the bit is '0', the master device is writing data to the FM24C256. The control bit at the lowest address allows the microcontroller to specify the operation type, ensuring that the correct action is taken based on the intended operation.

The MM36SB020 chip complements the FM24C256 by providing storage for Chinese characters in a 16x16 dot matrix format. It is essential for applications that require the display of Chinese characters on screens or other output devices. The control commands for the MM36SB020 are crucial for managing how characters are stored, retrieved, and displayed, allowing for efficient rendering of text in applications where Chinese language support is necessary.

Overall, this configuration illustrates a typical use case of I2C communication for memory management and character display, showcasing the integration of different components to achieve a specific functionality in electronic systems.FM24C256 as shown 27-54 slave interface circuit I2C bus, the address format shown in Table 27-3. A2, Al, AO is set to low (when extended storage capacity, the need to change A2 , A1, AO setting), the lowest address to write control bit, which is. 1 expressed a read operation from the device as a o indicates to be a slave write operation start signal is sent from the controller MCU and after the device address byte. FM24C256 monitors the bus, when its address is sent from the device to match the address when, in response to a signal should blame; perform the appropriate read/write operation according to the state read and write control Pina bit R/Ws.

MM36SB020 chip for storing 16 16 dot matrix Chinese character. Control commands are shown in Table MM36SB020

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713