FOLDBACK CURRENT LIMITER

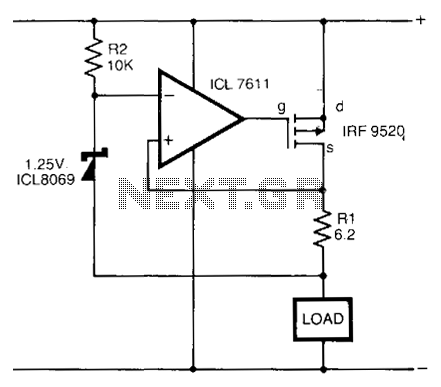

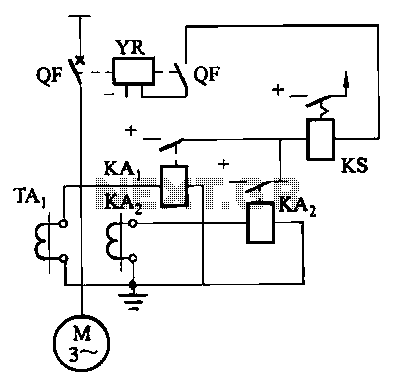

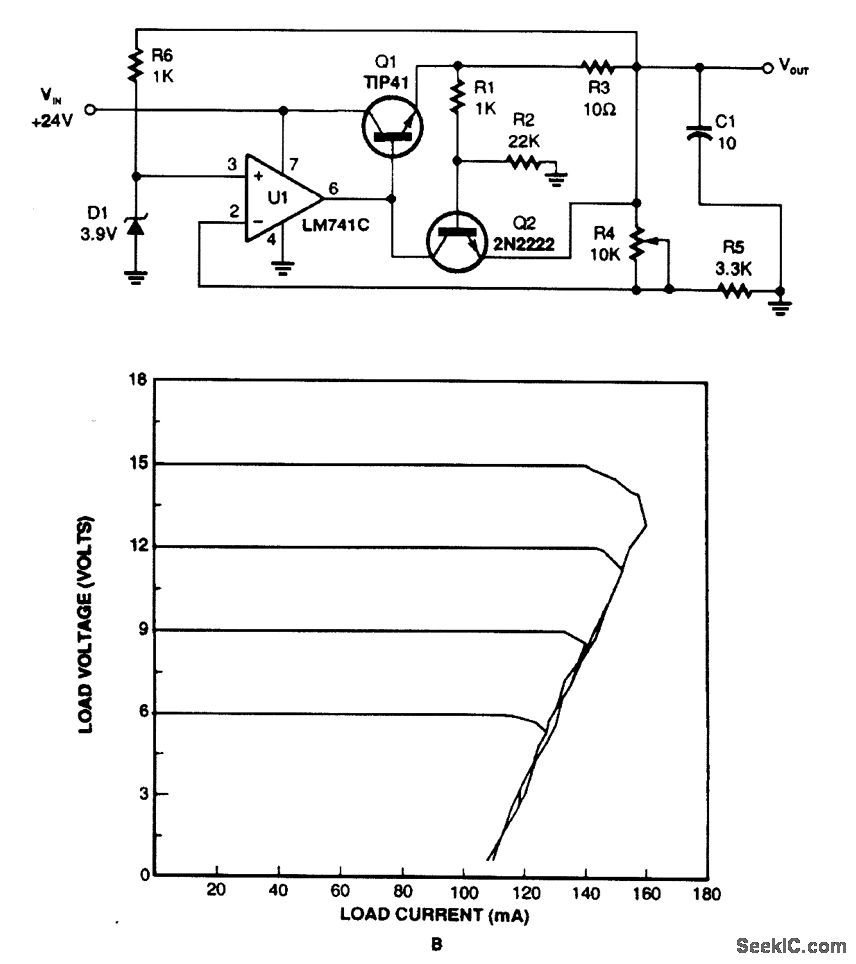

This regulator utilizes the voltage drop across resistor R3 to monitor current draw. When the current exceeds a certain threshold, Q2 is activated, which in turn disables Q1 and reduces the output voltage. Current limiting takes place when Q2 experiences 0.65 V across its base-emitter junction. The circuit exhibits foldback characteristics, as illustrated in the accompanying figure.

The described regulator circuit is designed to provide robust current limiting features, which are essential in protecting both the power supply and the load from excessive current conditions. The operational mechanism is based on the interaction between the components, particularly the resistors and transistors.

Resistor R3 plays a crucial role in sensing the current flowing through the load. As the load current increases, the voltage drop across R3 also increases. Once this voltage reaches a predetermined level, specifically 0.65 V, it activates transistor Q2. The activation of Q2 serves as a feedback mechanism that regulates the output voltage by turning off Q1, which is responsible for supplying power to the load.

This feedback loop is vital for maintaining circuit stability and preventing damage due to overcurrent situations. The foldback characteristics of the circuit allow for a reduction in output voltage as the current draw increases beyond the set limit. This behavior helps to minimize power dissipation in the circuit and enhances the overall efficiency.

It is important to note that the foldback feature not only protects against current surges but also aids in thermal management by reducing the output power delivered to the load under fault conditions. The design of such a regulator circuit is particularly advantageous in applications where the load may experience sudden changes in current demands, ensuring that the system remains within safe operational limits while providing reliable performance.This regulator uses the drop across R3 to sense current draw, turning on Q2, removing drive from Q1, and lowering the output voltage. Limiting occurs when Q2 has 0. 65 V across the base-emitter junction. This circuit has foldback characteristics as seen from the figure. 🔗 External reference

The described regulator circuit is designed to provide robust current limiting features, which are essential in protecting both the power supply and the load from excessive current conditions. The operational mechanism is based on the interaction between the components, particularly the resistors and transistors.

Resistor R3 plays a crucial role in sensing the current flowing through the load. As the load current increases, the voltage drop across R3 also increases. Once this voltage reaches a predetermined level, specifically 0.65 V, it activates transistor Q2. The activation of Q2 serves as a feedback mechanism that regulates the output voltage by turning off Q1, which is responsible for supplying power to the load.

This feedback loop is vital for maintaining circuit stability and preventing damage due to overcurrent situations. The foldback characteristics of the circuit allow for a reduction in output voltage as the current draw increases beyond the set limit. This behavior helps to minimize power dissipation in the circuit and enhances the overall efficiency.

It is important to note that the foldback feature not only protects against current surges but also aids in thermal management by reducing the output power delivered to the load under fault conditions. The design of such a regulator circuit is particularly advantageous in applications where the load may experience sudden changes in current demands, ensuring that the system remains within safe operational limits while providing reliable performance.This regulator uses the drop across R3 to sense current draw, turning on Q2, removing drive from Q1, and lowering the output voltage. Limiting occurs when Q2 has 0. 65 V across the base-emitter junction. This circuit has foldback characteristics as seen from the figure. 🔗 External reference